Part Number: AM2634-Q1

Other Parts Discussed in Thread: AM2634

Previous inquiry:

e2e.ti.com/.../am2634-q1-is-there -any-register-or-memory-without-erase-at-warm-booting/4378125#4378125

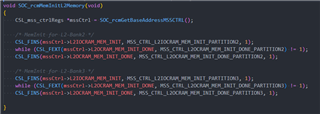

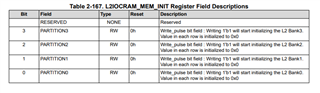

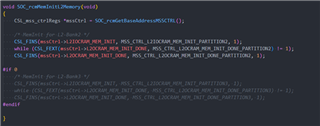

From previous inquiries, I found out that for QSPI_SBL, the upper 1MB area is initialized.

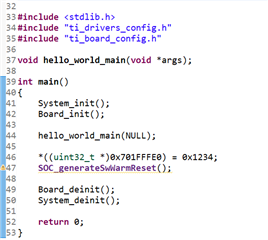

To confirm the above, after writing the signature in the 0x701FFFE0" area in QSPI_SBL, we executed "SOC_generateSwWarmReset" and confirmed that the signature is maintained.

However, we have confirmed that the data in the "0x701FFFE0" area is not maintained when "SOC_generateSwWarmReset" is executed in the following cases.

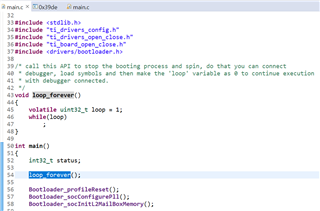

1. Load Application SW image from External Flash.

2. Run Application SW by executing "Bootloader_runSelfCpu".

3. Write a signautre in the "0x701FFFE0" area.

4. QSPI_SBL is done again by running "SOC_generateSwWarmReset".

5. Check "0x701FFFE0".

In the case above, we confirmed that the "0x701FFFE0U" area is initialized to 0.

I would like to set some kind of signature to further differentiate the purpose of the reset.

In this case, is there a way for Application to pass data to QSPI_SBL?