Other Parts Discussed in Thread: SYSCONFIG

Hi,

May I know:

1, May I know if I can select anyone instance if I used only core0?

2, What is the map of intr_num with instance since I'd like ti register ISR?

in this example,

GPIO Pins in AM263x:

AM263x has 139 GPIO pins

The device has four instances of the GPIO module, one dedicated per R5FSS processor core

- Pinmux/IOMUX allows assignment of GPO pin control to a specific R5FSS processor core using a 4:1 MUX (MCUSDK sysconfig generates code automatically for configuring this)

- GPI pins are observable by all processor cores

The GPIO modules are capable of supporting a maximum of 144 dedicated pins. AM263x implements 139 pins.

GPIO Interrupts in AM263x:

Regarding interrupts,

From the GPIO modules, 180 events/interrupts reach as input to GPIO Interrupt XBAR as shown in diagram below.

The 180 inputs contain both the individual GPIO interrupts (144 muxed from 4 GPIO modules) and also the 9 bank interrupts of 4 GPIO module

| Number of Interrupts | |

| Single GPIO Pin Interrupts | 144 |

| GPIO Bank Interrupts for instance 0 | 9 |

| GPIO Bank Interrupts for instance 1 | 9 |

| GPIO Bank Interrupts for instance 2 | 9 |

| GPIO Bank Interrupts for instance 3 | 9 |

| Total Interrupts | 180 |

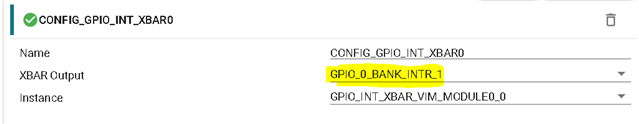

In the Current SDK 8.5 we have gpio_input_interrupt example using GPIO bank interrupt.

In the example Go to SysCfg --> GPIO INT XBAR Option.

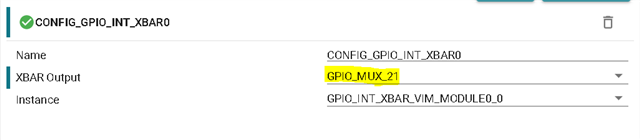

To use the Individual GPIO Interrupt, change the XBAR Output option to respective GPIO_MUX pin required for you. Here ignore the "_MUX" in this context, this refers to the individual GPIO Pin only.

While acknowledging and checking the interrupt status for Individual and Bank GPIO Interrupts these APIs can be used:

| GPIO Bank | Individual GPIOs |

| GPIO_getBankIntrStatus | GPIO_getIntrStatus |

| GPIO_clearBankIntrStatus | GPIO_clearIntrStatus |