I've integrated the Diagnostic Library source code into my current project, and I am only running the SL_SelfTest_CAN CAN_ECC_TEST_MODE_1BIT test on DCAN1 RAM. The issue I see is that when the 1Bit fault is created by reading from the corrupted data location, the fault that occurs is usually flagged with DEFLG instead of SEFLG in the DCAN1 ECC CS register (although sometimes it is correctly flagged with SEFLG). Pseudo-code from my startup procedure is below. Any guidance on how to correct this issue is greatly appreciated. Thanks!

Initialize Core Registers

Initialize Stack Pointers

Enable clocks to peripherals and release peripheral reset

Identify the source of the last reset

Initialize memory

Enable CPU Event Export

Check if there were ESM group3 errors during power-up

Initialize System - Clock, Flash, device-level multiplexing and I/O multiplexing settings

Back up DCAN1 Control register

Clear CAN_INIT_BIT, and enable ECC in DCAN1 Control register

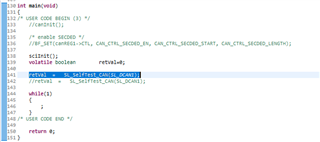

Run SL_SelfTest_CAN CAN_ECC_TEST_MODE_1BIT test on DCAN1

Restore DCAN1 Control register