Required schemaic review of board design based on TMS5704357BGWTEP and TMS5701224CpGEQQ1.

Mainly for EMIF parallel bus external flash and External SRAM is connected. Ethernet & clock section.

Regards,rtc987r1_08mar2023_For Review.pdf

Amit

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Required schemaic review of board design based on TMS5704357BGWTEP and TMS5701224CpGEQQ1.

Mainly for EMIF parallel bus external flash and External SRAM is connected. Ethernet & clock section.

Regards,rtc987r1_08mar2023_For Review.pdf

Amit

HI, The complete schematic is not same as TI HDK.

TI HDK is using SDRAM, we have connected external flash, SRAM and FPGA on EMIF bus. Review of that portion is mainly required.

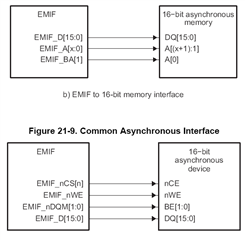

As per reference manual ther is limitation of using A0 & A1 lines 16 bit or 8 bit addressing. Thus, Kindly review EMIF section.

All the memories connected to EMIF (external flash, SRAM and FPGA) are async memories.

The EMIF address pin EMIF_A[0] always provides the least significant bit of a 32-bit word address. Therefore, when interfacing to a 16-bit asynchronous device, the EMIF_BA[1] pin provides the least-significant bits of the halfword or byte address.

The EMIF BA[1] should be connected to A0 of memory chip.

Change noted.

Kindly Review the schematic portion Ethernet PHY and Magnetics. The PHY Device used here is TI device DP83848EP.

Hi Amit,

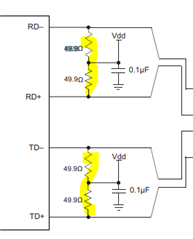

I am not very familiar with DP83848EP. The datasheet suggests to place the 49.9-Ω,1% resistors, and 0.1-µF decoupling capacitor, near the PHYTER TD± and RD± pins.

The magnetics have a large impact on the PHY performance. You can ask DP83848 experts to review the circuitry around the PHY and get recommendation of magnetics.

https://e2e.ti.com/support/interface-group/interface/f/interface-forum