Part Number: MSPM0L1304

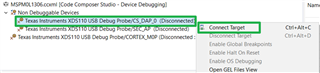

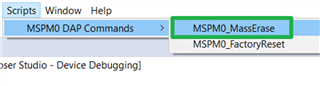

I want to set the core in halt to execute the flash mass erase .

Here below my sequence:

- I power on the component while keeping NRST pin low.

- I send sequence to enter in SWD mode and read IDCODE (it's correctly read as 0x0BB11477).

- I write in DHCSR: DBGKEY, C_HALT and C_DEBUGEN

- I set the NRST pin high

- I read DHCSR (to check if the core is in halt state) but SWD not response.

if I try to read the DHCSR with NRST low I always read 0x00.

Could you please send me the sequence to halt the core?

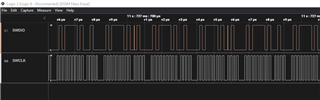

Could you provide a me a logic sample of this sequence(such as saleae).

Thank you in advance.