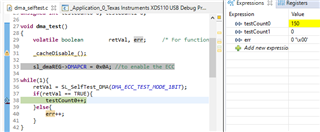

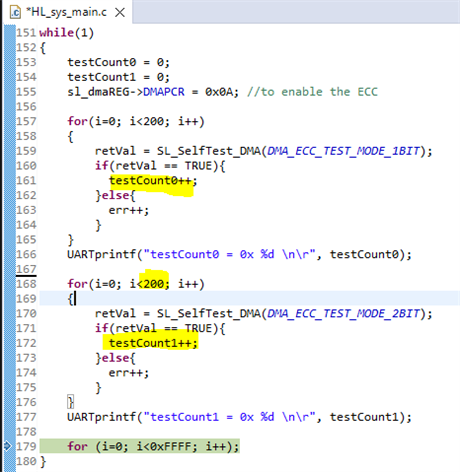

I'm experiencing exactly the same issue with the DMA ECC 1-Bit Self-Test that was reported in this (locked) thread: https://e2e.ti.com/support/microcontrollers/arm-based-microcontrollers-group/arm-based-microcontrollers/f/arm-based-microcontrollers-forum/1097304/tms570lc4357-dma-ecc-test-fails-randomly/4064481?tisearch=e2e-sitesearch&keymatch=TMS570LC4357%20DMAECCSBE#4064481

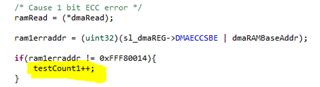

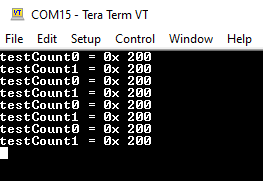

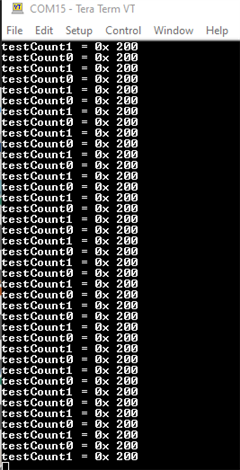

I tried using dmaBadECC=0xFFF80014 instead of 0xFFF80010 as suggested in the thread, but DMAECCSBE still reported the wrong address randomly.

Can you please help?

Thanks,

Cameron