Hi,

I'm currently working with the RM46 and TMS570. I'm trying to understand the EMAC module.

In section 31.2.17.1.1 of RM46xx datasheet, it is stated that "the EMAC issues an interrupt to the CPU when it writes the packet’s last buffer descriptor address to the appropriate channel queue’s transmit completion pointer located in the state RAM block"

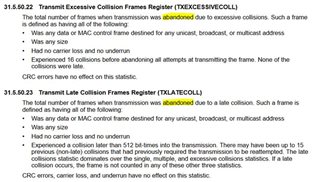

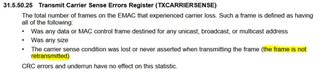

However, what happens if the transmission is abandoned? Following the datasheet, this could happen :

Is the completion pointer updated in the case transmission is abandoned? Or should I say, will the interrupt routine be entered for the abandoned packet?

Please note that I've read this thread: https://e2e.ti.com/support/microcontrollers/arm-based-microcontrollers-group/arm-based-microcontrollers/f/arm-based-microcontrollers-forum/1214441/rm46l850-emac-tx-completion-pointer-in-case-of-transmit-error/4595490

but the response is not clear.

Thanks for your time,

.....