Other Parts Discussed in Thread: HALCOGEN

Hello,

I am trying to generate a CRC on Flash memory using the SL_CRC_Calculate() function. However, I cannot find a way to access the origin or start address of the .cinit section in memory. I know the linker provides the symbols __TI_CINIT_Base and __TI_CINIT_Limit, but this does not cover the whole .cinit section as can be seen from the map file:

SECTION ALLOCATION MAP

output attributes/

section page origin length input sections

-------- ---- ---------- ---------- ----------------

.kernelTEXT

* 0 00000020 00005604

00000020 00002f04 os_tasks.obj (.kernelTEXT)

00002f24 000012dc os_queue.obj (.kernelTEXT)

00004200 00000818 os_event_groups.obj (.kernelTEXT)

00004a18 000004b0 os_portasm.obj (.kernelTEXT)

00004ec8 000003e0 os_port.obj (.kernelTEXT)

000052a8 0000037c os_heap.obj (.kernelTEXT)

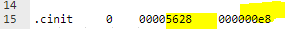

.cinit 0 00005628 000000e8

00005628 0000009d (.cinit..data.load) [load image, compression = lzss]

000056c5 00000003 --HOLE-- [fill = 0]

000056c8 0000000c (__TI_handler_table)

000056d4 00000009 (.cinit..kernelBSS.load) [load image, compression = lzss]

000056dd 00000003 --HOLE-- [fill = 0]

000056e0 00000008 (.cinit..bss.load) [load image, compression = zero_init]

000056e8 00000008 (.cinit..kernelHEAP.load) [load image, compression = zero_init]

000056f0 00000020 (__TI_cinit_table)

...

GLOBAL SYMBOLS: SORTED BY Symbol Address

address name

------- ----

00000000 resetEntry

....

0000560c vPortInitialiseBlocks

00005628 __TI_static_base__

000056c8 __TI_Handler_Table_Base

000056d4 __TI_Handler_Table_Limit

000056f0 __TI_CINIT_Base

00005710 __TI_CINIT_Limit

Notably, there's __TI_static_base__ and __TI_Handler_Table_Base in between the end of the previous section (ends @ 0x5628) and the __TI_CINIT_Base (0x56f0).

I wasn't able to find any documentation on __TI_static_base__, and couldn't find any confirmation that the Handler table will always appear before the Cinit table. Is there a way to capture the whole of the .cinit section?

Thank you!