Hello,

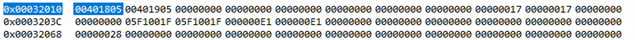

I'm trying to write my own Switch Implementation on the PRU. For this I have written assembler code to test sending and receiving data over Ethernet. Receiving works, but I can't get the PRU to send data. For both ways I am using the L1 FIFO and the R30/R31 Interface. In Register 0x300B 2068 I can clearly see the FIFO filling up, but it never gets emptied. I already tried setting TX_ENABLE manual after filling the FIFO, but it seems like TX_EN never gets asserted.

From the Refernce Manual I understand, that TX_EN is automatically set, when these conditions are met:

1. TX L1 FIFO not empty

2. Interpacket gap (IPG) timer expiration

3. RX_DV to TX_EN timer expiration

4. TX_EN compare timer expiration

As far as I can tell, all these Requirements are met, so I can't figure out, why the FIFO is not being emptied.

So here are a few questions that might get me further with my problem:

1. What are the minimal requirements for sending data to the MII? Do I need to send a valid frame or would some Bytes of 0xFF still get processed further? Do I need to configuere a MAC and MDIO?

2. Where can I read, if RX_DV or TX_EN is set? Where can I see if the above named timers are expired?

Also during my research I found this in the Refernce Manual on page 3261:

4.11.2.4.1.1.4.1 TX Preemption Programming Model

Start a new frame.

1. Wait until R31.TX_EOF event

2. Load data into TX L2 FIFO until the full frame is completed

3. Issue a R30.TX_EOF + TX_CRC_HIGH + TX_CRC_LOW

Shouldn't it be R31 instead of R30?

Thanks in advance for your answer.

Best regards

Marius Apostel