Hello.

I'm trying to receive and transmit with a SCI device using the DMA to transfer data to the RAM. In my operational case I will receive burst of data from others equipment to my SCI devices and I will poll in a period thread the received data (and maybe send some data too).

I’m facing two problems that concern the receiving part.

- First issue

What I did:

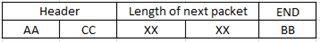

- Setup a dma transfer from the SCI device to a buffer. With elements of 8bits, one element per frame, the size of the buffer in bytes as the number of expected frame and auto-initialization.

- Setup the SCI device in loopback mode and send data to SCI device using a DMA transfer.

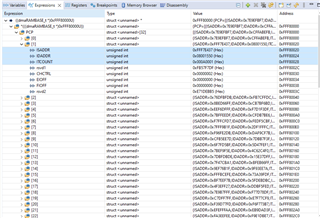

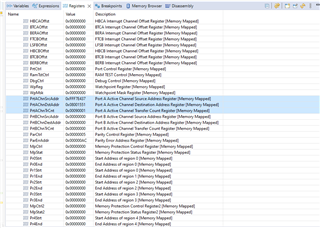

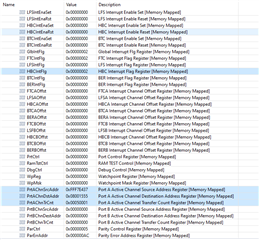

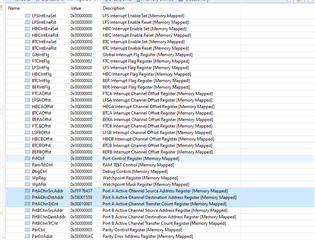

- To retrieve received data, I read the CDADDR register.

I observed that the value in the CDADDR register is always ‘late’ and do not point to the last transferred byte. In fact, the CDADDR register will not change until a new data burst is received.

The datasheet SPNU563A, explain about the Working Control packet that: “These bits are only updated after a channel is arbitrated out of the priority queue”.

Therefore, I guess that the CDADDR register behavior is normal, but what is the correct way to received burst of data using the DMA?

In this topic DMA working control packet semantics - Arm-based microcontrollers forum - Arm-based microcontrollers - TI E2E support forums, I saw that I could use the PAACDADDR register to determine the real last written address. In fact, this work but I am not sure that this is the right way to do things.

- Second issue

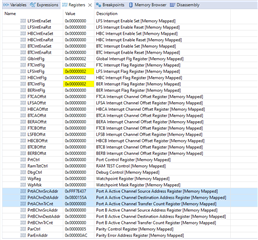

When the CDADDR register is up to date, I also observe a weird behavior. For example, a buffer of 10 bytes with addresses 0 to 9.

When the last burst of data fill the buffer until the address 8, then the CDADDR register point to the address 9.

When the last burst of data fill the buffer until the address 9, then the CDADDR register point to the address 9 too!

The only way a found to differentiate the two cases is with a BTC interruption. But again, I am not sure that this is the right way to do things.

Regards,

Jeff