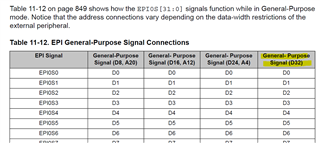

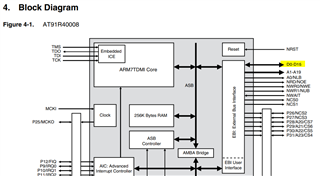

I am porting a legacy design from an AT91R40008. It has a very good External Peripheral Interface. I have 5 devices for the TI EPI Interface. One requires 16bit access and four require 8bit.. The only option appears to be the General-Purpose mode, using the address lines to enable the chips.

Can I map each range for the correct (and different bit access) and make it available at the same time?

Is there any example code that shows how to configure this?