Hi team,

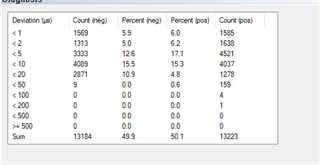

1)Using the Beckhoff SCC Demo, the FreeRTOS task is used to simulate the PDI and Syn0 interrupts, it seems that the DC function of EtherCAT can be implemented, but it don't work properly with the DC function, Sync Error for 1C32/1C33.20, there are errors, and the DC sync jitter is very large, essentially greater than 500us.

The customer then replaced it with a real PDI and Syn0 interrupt and found that in DC sync mode, the PDI interrupt could occur continuously while the Syn0 interrupt only occurs once. It doesn't come up anymore. Why;s this and how to get the Syn0 interrupt to occur continuously?

2) When using the DC function, continuously monitor the DC system clock of 0x0910 for EtherCAT and see that this clock can initially be the same as TwinCAT's PC clock, but will be about 20 seconds faster than the PC clock after 10 minutes of operation. The longer the time, the faster.

Could you help check this case? Thanks.

Best Regards,

Cherry