Hi All,

I am using TMS570LC43 MCU with safeTI Diagnostic Library and integrate with RTOS.

In afterSTC() function

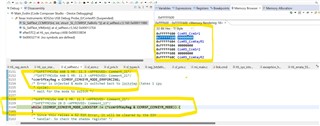

Code reach to the SL_SelfTest_VIM(VIM_SOFTWARE_TEST); function and fail inside this function.

Here the inside the "tmp = SL_SelfTest_CCMR5F(CCMR5F_CPUCOMP_ERROR_FORCING_TEST, TRUE, &failInfoCCMR5F);"

*ccmr5fKeyReg = CCMR5F_CCMKEYR_MODE_ERRFORCING; <-- the value inside "CCMkeyR1" register 0xfffff604 is 0

while (CCMR5F_CCMKEYR_MODE_LOCKSTEP != (*ccmr5fKeyReg & CCMR5F_CCMKEYR_MODE)) {

stuck here and system is going to SW reset.

}

Can you please tell what is the reason behind that, we have already did viminit();

Both SL_SelfTest_VIM(VIM_SOFTWARE_TEST); and SL_SelfTest_DMA(DMA_SOFTWARE_TEST); failing

Thanks

Pankaj Verma