Part Number: RM48L952

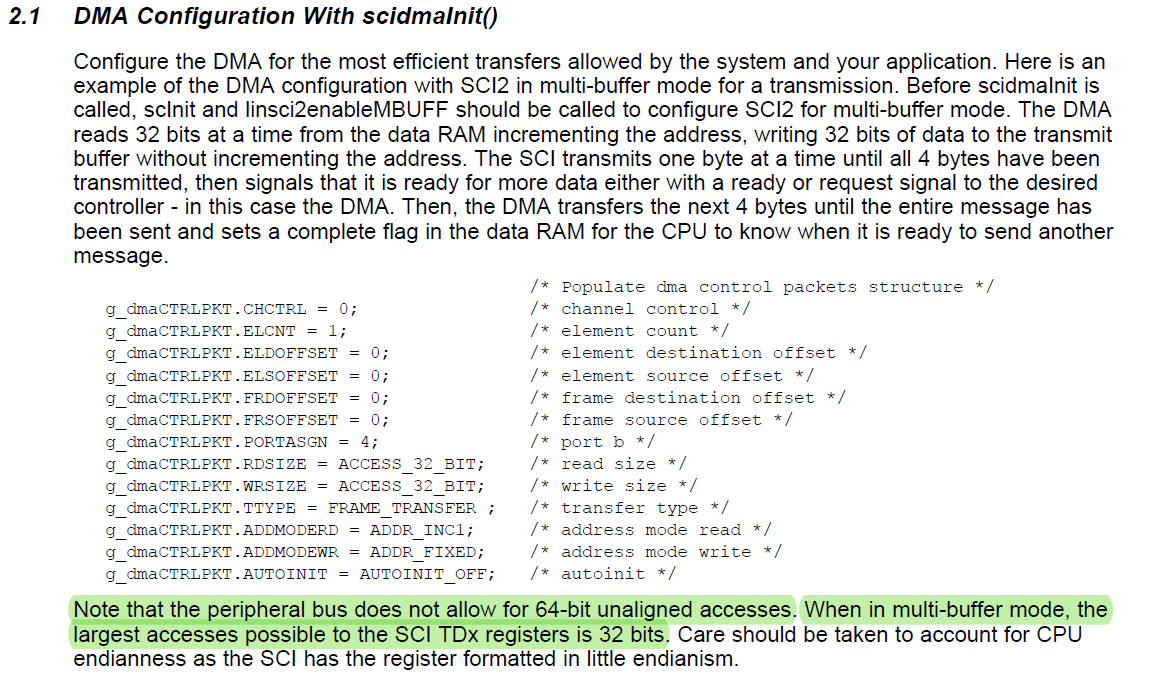

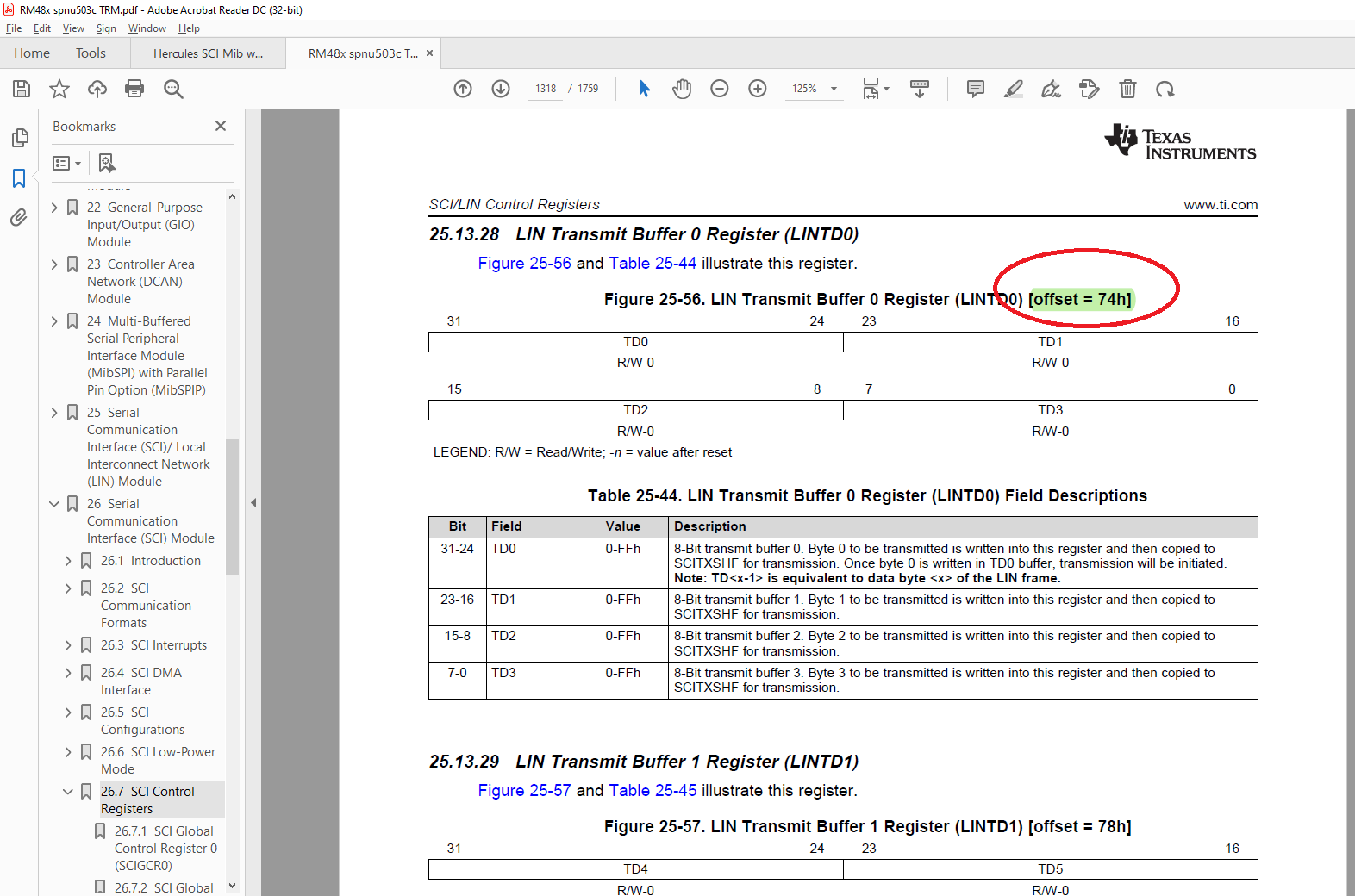

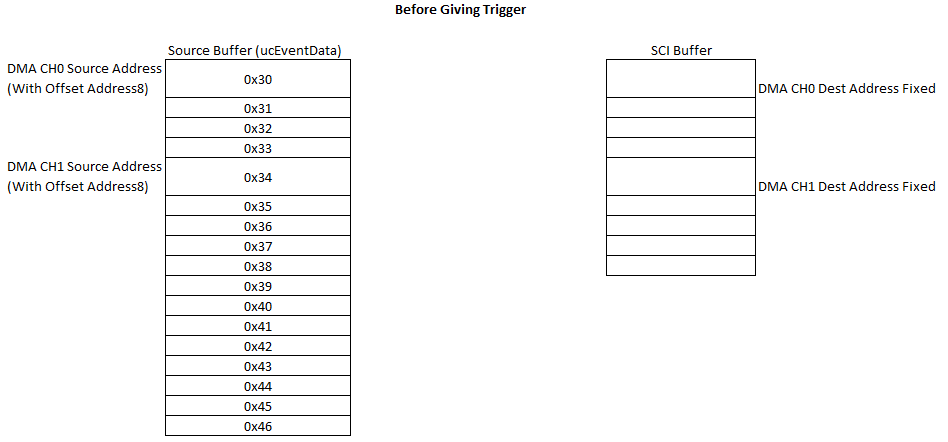

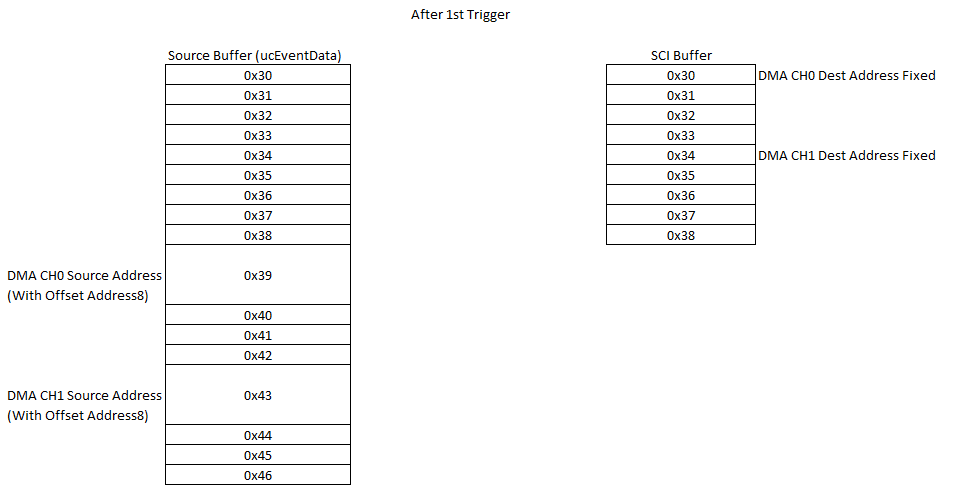

When i was writing multi-buffered SCI using DMA in SCI2 Driver. However, my code was able to transmit up to 4 bytes, but when I tried to transmit 8 bytes, the RM48L952 stopped working. Even if I check the datasheet, it seems that there is buffer space and 8 Byte transmission is possible, but it does not work properly.