Part Number: TMS570LS3137

Hello everyone! I have a doubt about my bootloader program. The program is working fine. I was able to record a simple program. But now, I want to record another program, that uses FreeRTOS. I generated the .bin and modified the sys_link, and then I recorded this new program with FreeRTOS. But when I want to run the new program with FreeRTOS, the bootloader always enters in the section: svcEntry b svcEntry I really need help with this issue. I don't know what I can do to fix it.

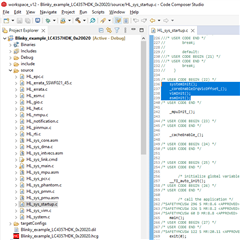

I copied the sys_link.cmd from my FreeRTOS program:

-retain="*(.intvecs)"

/* USER CODE BEGIN (1) */

/* USER CODE END */

/*----------------------------------------------------------------------------*/

/* Memory Map */

MEMORY

{

VECTORS (X) : origin=0x00020020 length=0x00000020

FLASH_CODE (RX) : origin=0x00020040 length=0x008000-0x40 fill=0xFFFFFFFF

FLASH0 (RX) : origin=0x00028000 length=0x0014FFC0

FLASH1 (RX) : origin=0x00180000 length=0x00180000

STACKS (RW) : origin=0x08000000 length=0x00000800

KRAM (RW) : origin=0x08000800 length=0x00000800

RAM (RW) : origin=(0x08000800+0x00000800) length=(0x0003F800 - 0x00000800)

/* USER CODE BEGIN (2) */

/* USER CODE END */

}

/* USER CODE BEGIN (3) */

/* USER CODE END */

/*----------------------------------------------------------------------------*/

/* Section Configuration */

SECTIONS

{

.intvecs : {} > VECTORS

/* FreeRTOS Kernel in protected region of Flash */

.kernelTEXT : {} > FLASH0 | FLASH1

.cinit : {} > FLASH0 | FLASH1

.pinit : {} > FLASH0 | FLASH1

/* Rest of code to user mode flash region */

.text : {} > FLASH0 | FLASH1

.const : {} > FLASH0 | FLASH1

/* FreeRTOS Kernel data in protected region of RAM */

.kernelBSS : {} > KRAM

.kernelHEAP : {} > RAM

.bss : {} > RAM

.data : {} > RAM

}

Thank you so much.