Other Parts Discussed in Thread: HALCOGEN

Dear All,

How do you I configure the eQEP module edge capture unit to achieve the capture timer reset behaviour as described in SPNU515C–March 2018, page 903, sec 21.5 eQEP Edge Capture Unit?

"The eQEP capture timer (QCTMR) runs from prescaled VCLK4 and the prescaler is programmed by the

QCAPCTL[CCPS] bits. The capture timer (QCTMR) value is latched into the capture period register

(QCPRD) on every unit position event and then the capture timer is reset, a flag is set in

QEPSTS:UPEVNT to indicate that new value is latched into the QCPRD register. Software can check this

status flag before reading the period register for low speed measurement and clear the flag by writing 1."

Our configuration is not working are expected, i.e., reset of QCTMR happen on every position event.

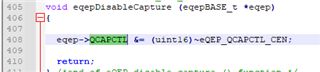

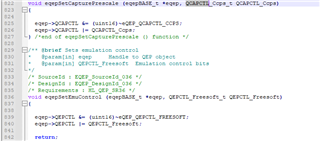

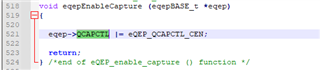

Current configuration code for the capture timer sets the memory mapped register QCAPCTL bits in the following sequential order :

- Write 1 to bit QCAPCTL[15] (enable capture unit)

- Write 0 to bits QCAPCTL[5..6] (= CAPCLK = VCLK4/2)

- Write 1 to bit QCAPCTL[4] (= CAPCLK = VCLK4/2)

- Write 0 to bits QCAPCTL[0..3] (= UPEVNT = QCLK/1)

Thanks for your time and support.

With my best regards,

Luis