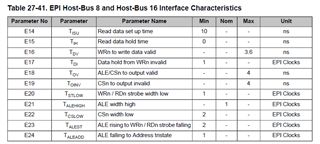

We have an external 30.72Mhz clock input to the TMC4, We output this clock to a FPGA and a couple of duarts. The duarts are async, but the clock is fed into the FPGA to synchronize it with the TM4C. We do not want to, if possible, change the FPGA code, and are trying to synthesize a test model to see if the read and writes will work. We need to know/understand the timing relationship between the EPI clock and the read and write lines.

For Host 16 EPI mode (yes it's async), What is the /RD and /Write setup and hold times relative to the system clock?