Hello,

In my project, I'm using 3 DMA channels assigned to 3 UART TX channels. The rest of the DMA channels should be unused. I have a requirement to ensure register writes and I'm doing it following way:

void WriteAndRead(volatile uint32_t* const pReg, const uint32_t value)

{

*pReg = ((uint32_t)value);

volatile uint32_t actualValue = *pReg;

if ((actualValue & value) != value)

{

ErrorRaise(value, actualValue, *pReg, pReg)

}

}

With the above code, I'm able to capture errors with really rare occurrence rates and with for example calling parameters ((uint32_t*)0xfff80030, 0xe) and the following error parameters:

1: 0xe,

2: 0x0,

3: 0xe,

4:0xfff80030

So it seems that the CPU is not blocked until the write to Control Packet RAM is finished and the first read operation (param 2) is not returning an expected value. But after a few clock cycles, the correct value is observed (param 3).

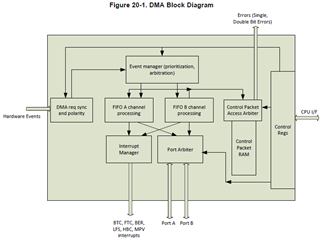

In Technical Reference Manual SPNU563A I found the following information

"20.3.2 Channel Configuration":

"- The RAM is accessible by queue A and queue B state machines as well as CPU."

"- When there are simultaneous accesses, the priority is resolved in a fixed priority scheme with the CPU

having the highest priority."

My questions are:

- Is it a problem with the write or read operation? I need to ensure that all parameters are in place before the DMA transfer trigger.

- Can we estimate the maximum delay value that needs to be applied to ensure that data is in place?

- If applying some do-while() loop fix a problem or just hide it? Could you please describe some background of such behavior?

- From the reference manual it looks like SW access shall have the highest priority so I do not understand why this problem is visible.

Thank you for your help,

Regards,

Sebastian Sokolowski