Hello,

I have been observing an issue similar to https://e2e.ti.com/support/microcontrollers/arm-based-microcontrollers-group/arm-based-microcontrollers/f/arm-based-microcontrollers-forum/962007/ccs-tms570lc4357-branch-to-_c_int00-from-reset-vector-is-not-working/3558660?tisearch=e2e-sitesearch&keymatch=branch%25252520%25252526%25252526%25252520alignment#3558660

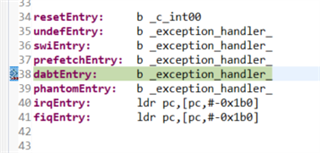

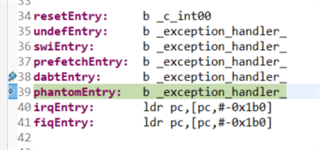

I have an exception handler written in assembly which is branched to following an exception.

For context, data aborts are generated as part of our startup self-test routine. During these data aborts, depending on the location of _exception_handler_, one of the following events occurs:

- Successfully branches to _exception_handler_.

- Rather than branching to _exception_handler_, PC is incremented to the next instruction (phantomEntry). At this point, debugging efforts become unpredictable (nRST causes a reset to a random location - not 0x0, "Resume" operations result in "step" operations, etc.)

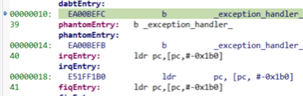

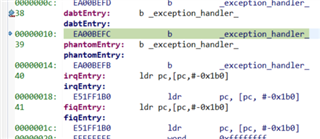

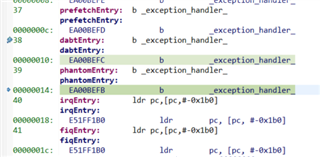

Note the screenshots below taken during a failure case.

A) Data abort is thrown.

B) Following an "assembly step into" operation, the PC is incremented to the next instruction rather than branching to _exception_handler_.

The documented success/failure cases can be seen below:

| _exception_handler_ Address | Test Outcome |

| 0x2FB98 | FAILS |

| 0x2FB9C | FAILS |

| 0x2FBA0 | FAILS |

| 0x2FC10 | FAILS |

| 0x2FC0C | FAILS |

| 0x2FC08 | FAILS |

| 0x2FC18 | PASSES |

| 0x2FC1C | PASSES |

| 0x2FC20 | PASSES |

| 0x2FC28 | PASSES |

| 0x2FC2C | PASSES |

| 0x2FC30 | PASSES |

| 0x2FC88 | PASSES |

| 0x30B08 | PASSES |

In addition, I have verified that the branch instruction is correct via the memory browser as well as the output .bin file during both the failure and success cases.

Any input would be greatly appreciated.

Thanks,

Grayson