Part Number: MCU-PLUS-SDK-AM243X

Other Parts Discussed in Thread: SYSCONFIG

Hello TI-Support,

I am currently using this interrupt/gpio example

gpio_input_interrupt_am243x-evm_r5fss0-0_nortos_ti-arm-clang

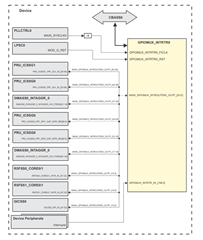

on my EVM board (AM243x). This works perfectly with the on-board button and the IRQ pin "SPI0_CS1/C13". Switching to a different GPIO pin "PRG0_PRU1_GPO13/T6" in conjunction with an externally fed square wave signal (e.g. 10 Hz) does not cause any problems, too. Unfortunately, I have not yet managed to change the example so that I can react to two IRQs. If I make the corresponding configurations in example.syscfg, I always get the following error message shortly after execution:

[MAIN_Cortex_R5_0_0] [Error] Sciclient event config failed!!!

ASSERT: 0.3018s: syscfg/ti_drivers_config.c:Sciclient_gpioIrqSet:143: FALSE failed !!!

I am probably not allowed to configure the second gpio pin like the first one? I'd appreciate any help. A simple example that can respond to more than one external gpio irq would also be great.

By the way, I'm currently using the following versions :

TI CCS: 12.5

SysConfig: 1.18.0

SDK: 9.0.0.35

Compiler: TI Clang v3.2.0.LTS

Best regards,

Thomas