What is GPIO?

The General-Purpose Input/output (GPIO) peripheral provides dedicated general-purpose pins that can be configured as either inputs or outputs.

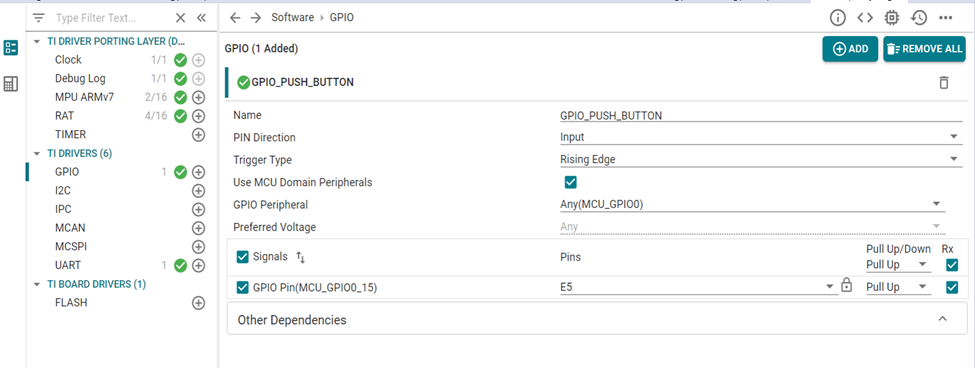

GPIO can be used in three modes:

*Input

*Output

*Interrupt

GPIO’s availability in the AM62X SDK:

The device has one or more instances of GPIO modules. The GPIO pins are grouped into banks (16 pins

per bank and 9 banks per module), which means that each GPIO module provides up to 144 dedicated

general-purpose pins with input and output capabilities; thus, the general-purpose interface supports up to 432 (3 instances × (9 banks × 16 pins)) pins. Since MCU_GPIO0_[23:143], GPIO0_[87:143], and GPIO1_[88:143] are reserved in this device, general purpose interface supports up to 198 pins.

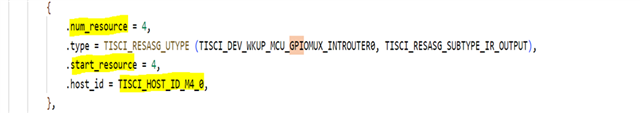

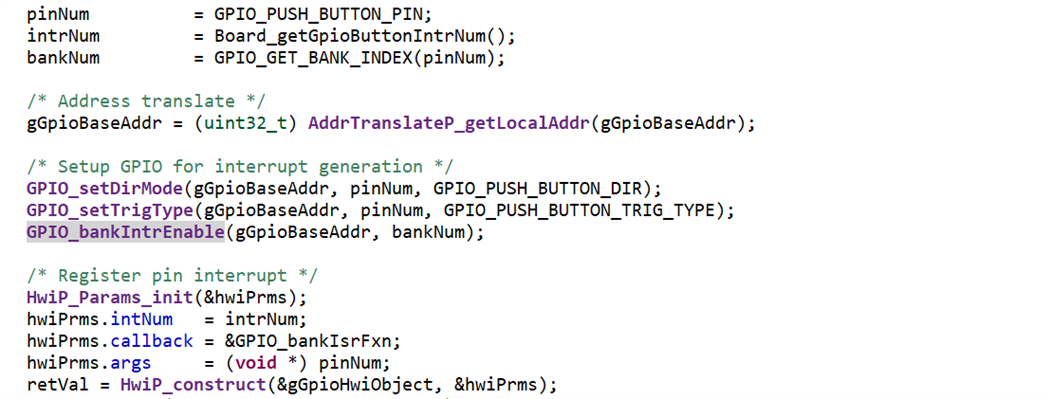

GPIO Interrupt Connectivity in AM62X SDK:

The SOC on the AM62 uses an interrupt router to route pin interrupts to the corresponding core for all GPIO pins. If you configure an interrupt for each pin, your design will be complicated. Therefore, the routing concept is designed to minimize the overhead of all GPIO interrupts in the SOC. So, user can control bank interrupts and individual pin interrupts.