Part Number: AM2634-Q1

Other Parts Discussed in Thread: AM2634

Dear Champs,

Are there any stable PLL values used for MCAL?

Or is there any improvement in PLL settings in MCALv9.0?

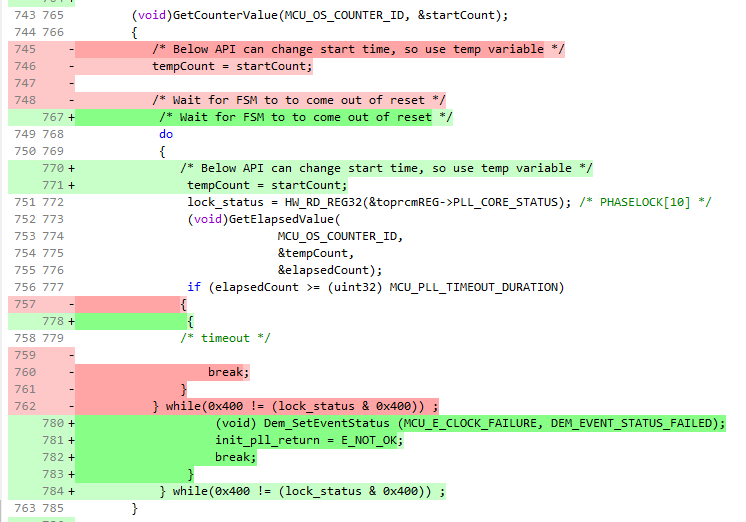

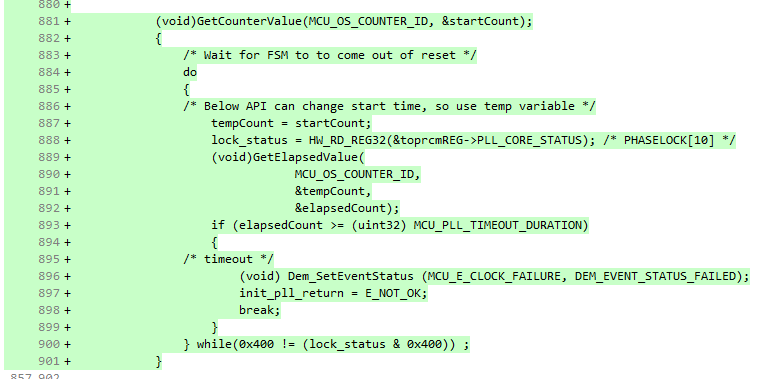

My customer is using MCAL v8.6.2 and faced boot fail issue in high temperature condition(85C Chamber test) and found the AM2634 was stuck as PLL locking was failed as below.

There is no issue when SBL in MCU+SDK was used.

Is there any difference in PLL setting values between MCU init in MCAL and SBL in MCU+SDK?

When customer checked VDD_CPU and clock, they could not find any issue yet. So, we want to check the optimal/Stable PLL value.

Please help on this.

Thanks and Best Regards,

SI.