Other Parts Discussed in Thread: SYSCONFIG

Hello,

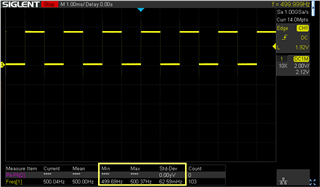

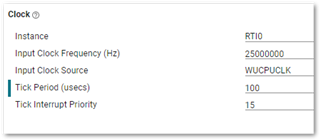

We need a 100us OS tick for our FreeRTOS implementation using the Clock configuration in SYSCONFIG. I see the default WUCPUCLK (25MHz on the EVM) is used for all the examples I've opened so far.

1) My understanding then is that we can generate the 100us tick with a resolution of 40ns (1 / 25MHz). Have I understood that correctly please? If so, this sounds plenty good enough to me.

2) Is there any merit to choosing a different clock source (e.g. DPLL_PER_HSDIV0_CLKOUT1) with a higher frequency to generate our 100us tick apart from the obvious higher resolution?

Thank you.