Hello,

Since CCS12.5, the following advice (rather its reverse) in C:/ti/mcu_plus_sdk_am263x_09_01_00_41/docs/api_guide_am263x/CCS_LAUNCH_PAGE.html doesn't work:

Using a simple SDK empty project, if I set 'mode = 0;' the console output suggests it is configuring for lockstep:

Cortex_R5_0: GEL Output: Loading Gel Files on R5F0 Cortex_R5_0: GEL Output: Gel files loading on R5F0 Complete Cortex_R5_0: GEL Output: ***OnTargetConnect() Launched*** Cortex_R5_0: GEL Output: AM263x Initialization Scripts Launched. Please Wait... Cortex_R5_0: GEL Output: AM263x_Cryst_Clock_Loss_Status() Launched Cortex_R5_0: GEL Output: Crystal Clock present Cortex_R5_0: GEL Output: AM263x_SOP_Mode() Launched Cortex_R5_0: GEL Output: SOP MODE = 0x0000000B Cortex_R5_0: GEL Output: Dev boot mode Cortex_R5_0: GEL Output: AM263x_Read_Device_Type() Launched Cortex_R5_0: GEL Output: EFuse Device Type Value = 0x000000AA Cortex_R5_0: GEL Output: AM263x_Check_supported_mode() Launched Cortex_R5_0: GEL Output: mode = 0 Cortex_R5_0: GEL Output: MSS_CTRL Control Registers Unlocked Cortex_R5_0: GEL Output: MSS_TOP_RCM Control Registers Unlocked Cortex_R5_0: GEL Output: MSS_RCM Control Registers Unlocked Cortex_R5_0: GEL Output: MSS_IOMUX Control Registers Unlocked Cortex_R5_0: GEL Output: TOP_CTRL Control Registers Unlocked Cortex_R5_0: GEL Output: ***R5FSS0 Reset for Lockstep *** Cortex_R5_0: GEL Output: *** R5FSS1 Reset for Lockstep *** Cortex_R5_0: GEL Output: R5F ROM Eclipse Cortex_R5_0: GEL Output: R5FSS0_0 Released Cortex_R5_0: GEL Output: R5FSS0_1 Released Cortex_R5_0: GEL Output: R5FSS1_0 Released Cortex_R5_0: GEL Output: R5FSS1_1 Released Cortex_R5_0: GEL Output: All R5F Cores Released for program load Cortex_R5_0: GEL Output: L2 Mem Init Complete Cortex_R5_0: GEL Output: MailBox Mem Init Complete Cortex_R5_0: GEL Output: *********** R5FSS0/1 Lockstep mode Configured******** Cortex_R5_0: GEL Output: CORE PLL Configuration Complete Cortex_R5_0: GEL Output: PER PLL Configuration Complete Cortex_R5_0: GEL Output: SYS_CLK DIVBY2 Cortex_R5_0: GEL Output: DPLL_CORE_HSDIV0_CLKOUT0 selected as CLK source for R5FSS & SYS CLKs Cortex_R5_0: GEL Output: CLK Programmed R5F=400MHz and SYS_CLK=200MHz Cortex_R5_0: GEL Output: *** Enabling Peripheral Clocks *** Cortex_R5_0: GEL Output: Enabling RTI[0:3] Clocks Cortex_R5_0: GEL Output: Enabling RTI_WDT[0:3] Clocks Cortex_R5_0: GEL Output: Enabling UART[0:5]/LIN[0:5] Clocks Cortex_R5_0: GEL Output: Enabling QSPI Clocks Cortex_R5_0: GEL Output: Enabling I2C Clocks Cortex_R5_0: GEL Output: Enabling TRACE Clocks Cortex_R5_0: GEL Output: Enabling MCAN[0:3] Clocks Cortex_R5_0: GEL Output: Enabling GPMC Clocks Cortex_R5_0: GEL Output: Enabling ELM Clocks Cortex_R5_0: GEL Output: Enabling MMCSD Clocks Cortex_R5_0: GEL Output: Enabling MCSPI[0:4] Clocks Cortex_R5_0: GEL Output: Enabling CONTROLSS Clocks Cortex_R5_0: GEL Output: Enabling CPTS Clocks Cortex_R5_0: GEL Output: Enabling RGMI[5,50,250] Clocks Cortex_R5_0: GEL Output: Enabling XTAL_TEMPSENSE_32K Clocks Cortex_R5_0: GEL Output: Enabling XTAL_MMC_32K Clocks Cortex_R5_0: GEL Output: ***All IP Clocks are Enabled*** Cortex_R5_0: AM263x

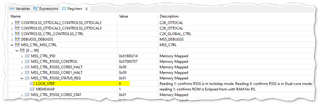

However, a quick check of the status reg and it is not in lock step, it is in dual core mode:

Please confirm.