Other Parts Discussed in Thread: SYSCONFIG, AM2434

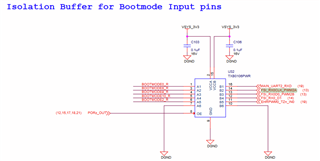

Hi,

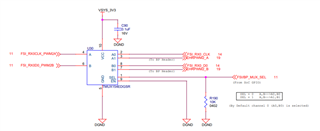

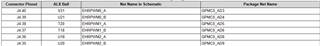

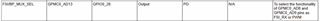

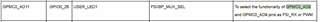

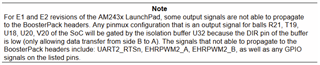

I'm trying to get the signals for EPWM2 channels A and B out to pins 35 and 36 of the Launchpad. I've set GPIO0_28 to HIGH, verified with GPIO_PinOutValue_Read(), but I'm still seeing no PWM signal for ePWM module 2.

Modules 0 and 1 are working fine. What am I missing?