Hi TI experts,

We are designing a system shown in picture below, where using MSPM0L1306 I2C0 as target PA0 & PA1 pins. pull-up resistor on salve side.

Since scl and sda is connected via a connector, so it would have hot swap scenarios.

To simulate some cases like plug in or plug out then accidently pull down scl or sda, we did a test, then encounter a problem.

Test:

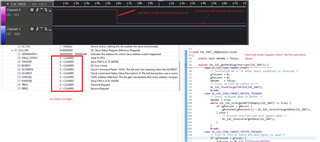

without connecting to other board, when MSPM0L1306 powered on with sda or scl pulled down, then disconnect with gnd, the line could not go back up. which means, master could not communicate anymore.

This happens when I2C module initialized with clock stretch enabled, if initialized with clock stretch disable, it could go back up.

I tested the example i2c_target_rw_multibyte_fifo_interrupts, it show the same result.

How to explain this situation, what happen to i2c module?

sdk version: mspm0_sdk_1_20_01_06

Thanks a lot for replying