Hi TI Experts,

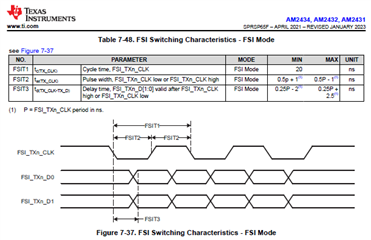

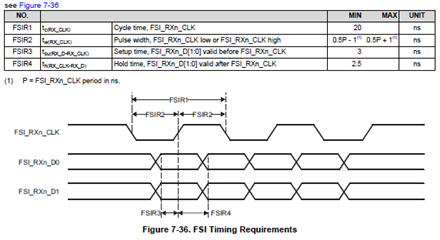

When FSI_CLK = 50MHz = 20ns,tSU_min (3ns) is greater than [tW_rxclk_min (0.5*20 - 1 = 9) -Td_max (0.25*20+2.5 = 7.5) = 1.5ns] , according to the values shown below.

Could you let me know if our calculation has any problem?

Thanks a lot!

Kevin