Part Number: TMS570LS1224

Tool/software:

Hello Jagasish,

I need to come back to this topic. I use the EEPROM Secors of the TMS570LS1224 as EEPROM Emulation useing my own wear leveinig Algorithm for man years now and it works fine so far. Now I want to EEC feature to get an ESM exception when the FEE gets corrupted.

Therefore I alredy use the Fapi_AutoEccGeneration mode and Multible of 8 Bytes for wehn writing to the FEE.

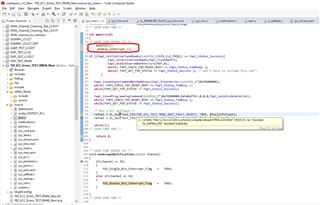

Fapi_issueProgrammingCommand((uint32_t*)u32_Addr, &(u8_Buffer[0]), u8_idx, NULL, 0, Fapi_AutoEccGeneration)

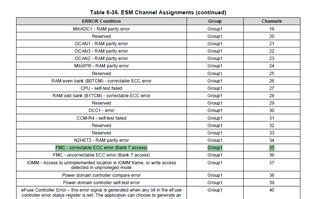

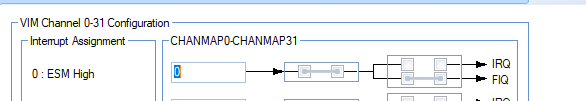

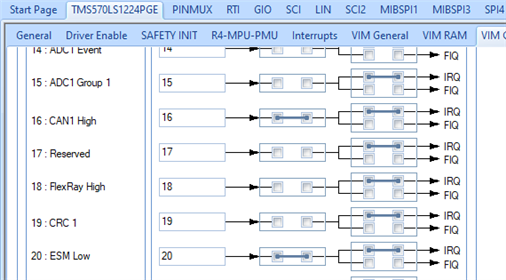

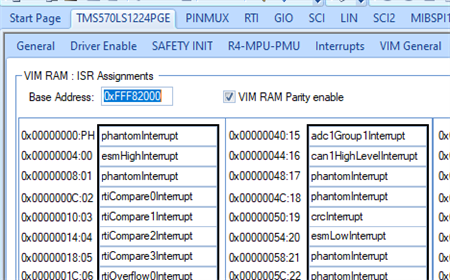

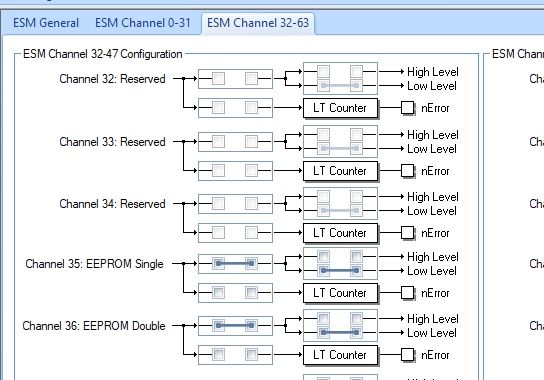

I configured the ESM like this:

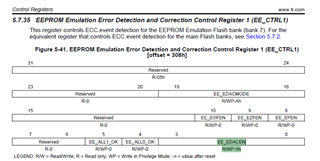

Now I tried to enable the ECC Error detection

Fapi_FmcRegistersType* p_FmcRegisters = F021_CPU0_BASE_ADDRESS;

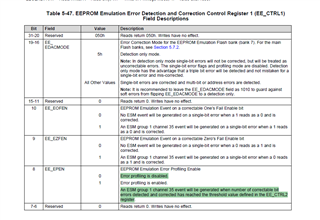

p_FmcRegisters->EeCtrl2.EE_CTRL2_BITS.EE_SEC_THRESHOLD = 1;

p_FmcRegisters->EeCtrl1.EE_CTRL1_BITS.EE_EDACMODE = 0x05; // Detection only mode

p_FmcRegisters->EeCtrl1.EE_CTRL1_BITS.EE_EOFEN = 1; // An ESM group 1 channel 35 event will be generated on

// a single bit error when a one reads as a zero and is corrected

p_FmcRegisters->EeCtrl1.EE_CTRL1_BITS.EE_EZFEN = 1; // An ESM group 1 channel 35 event will be generated on

//a single bit error when a zero reads as a one and is corrected

p_FmcRegisters->EeCtrl1.EE_CTRL1_BITS.EE_PEN = 1; // Error profiling is enabled.

// An ESM group 1 channel 35 event will be generated when number

// of correctable bit errors detected and corrected has reached

// the threshold value defined in the EE_CTRL2 register.

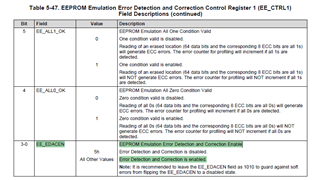

p_FmcRegisters->EeCtrl1.EE_CTRL1_BITS.EE_ALL1_OK = 1; // Reading of an erased location (64 data bits and the corresponding

// 8 ECC bits are all ones) will NOT generate ECC errors.

// The error counter for profiling will NOT increment if

// all ones are detected.

p_FmcRegisters->EeCtrl1.EE_CTRL1_BITS.EE_EDACEN = 0x0a; // Error Detection and Correction is enabled

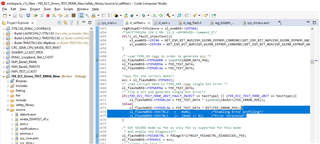

and try to trigger an ESM exception with the help of the Hercules Safety_Lib:

SL_SelfTest_Result fee_stResult;

bool b_Result = false;

b_Result = SL_SelfTest_FEE (FEE_ECC_TEST_MODE_1BIT_FAULT_INJECT, false, &fee_stResult);

b_Result = SL_SelfTest_FEE (FEE_ECC_TEST_MODE_2BIT_FAULT_INJECT, false, &fee_stResult);

The call of SL_SelfTest_FEE() returns true, but the fee_stResult is ST_FAIL and I do not get an ESM exception.

What do I miss?

Kind Regards

Jens