Tool/software:

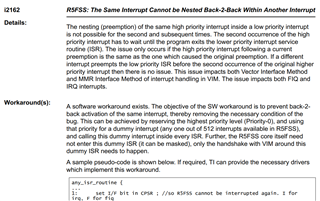

When a low priority IRQ interrupt continues to execute, a high priority interrupt can only be interrupted once

premise:There are only two different priority cycle timers in the system that interrupt IRQ1 and IRQ2, and IRQ1 has a higher priority than IRQ2;

operation:Perform a relatively long delay in IRQ1 to ensure that IRQ2 can be triggered multiple times during the delay period;

Phenomenon: No matter how long the IRQ2 delay event is, IRQ1 can only trigger an interrupt once during the IRQ2 delay period;

This phenomenon does not conform to the conventional understanding of interrupt nesting. If AM2732 has special requirements for this part, please explain. Otherwise, please assist in explaining the cause and solution of this phenomenon. thanks.