Other Parts Discussed in Thread: TMDS64EVM, TMDS243EVM, LP-AM243, SYSCONFIG

Tool/software:

Does the ICSS firmware support CRS and COL inputs for half-duplex in DUAL MAC and MII modes?

If so, how should the MCU+ SDK be modified for half-duplex in DUAL MAC and MII modes?

If not, is there a firmware that supports half-duplex in DUAL MAC and MII modes?

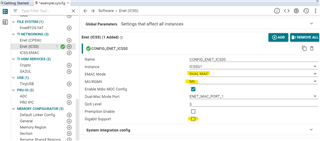

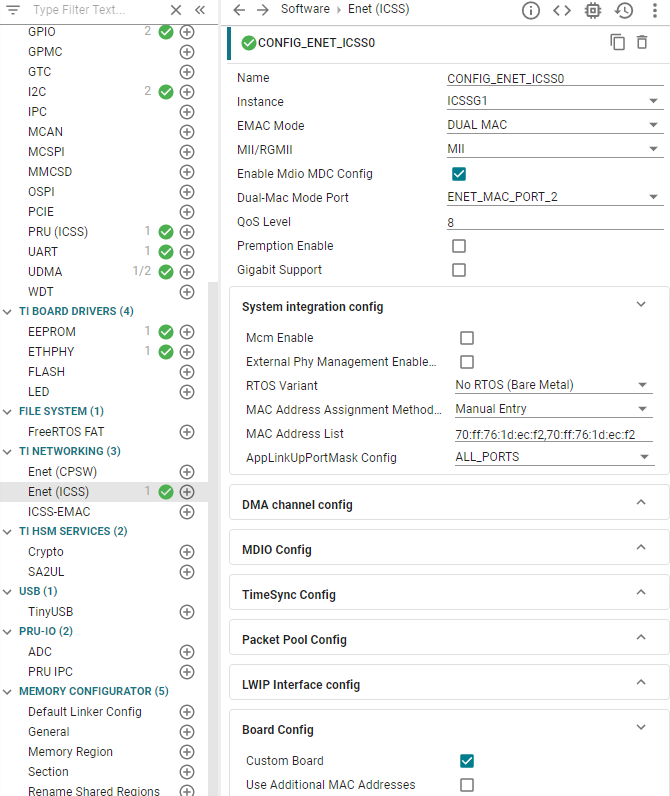

Our customer is trying to achieve half-duplex communication (10BASE-T1S) in DUAL MAC and MII modes based on the following example project in the MCU+ SDK.

AM243x MCU+ SDK 09.02.00.50: Enet Lwip ICSSG Example

C:\ti\mcu_plus_sdk_am243x_09_02_00_50\examples\networking\lwip\enet_lwip_icssg\am243x-lp

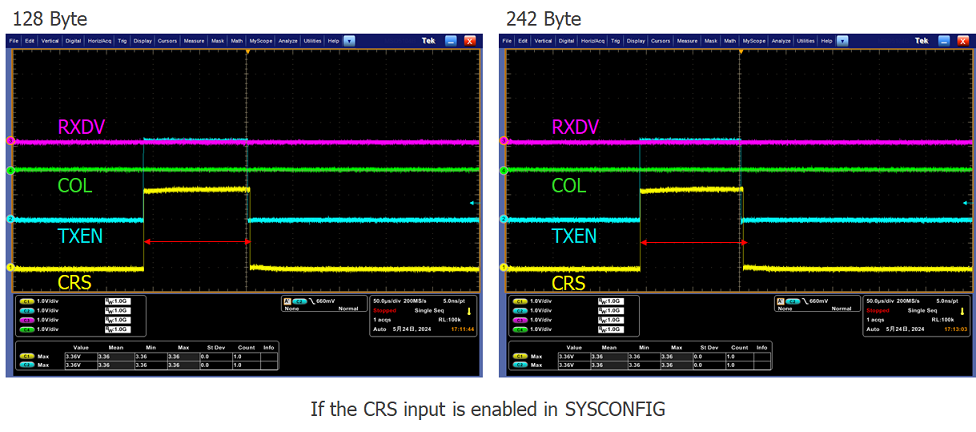

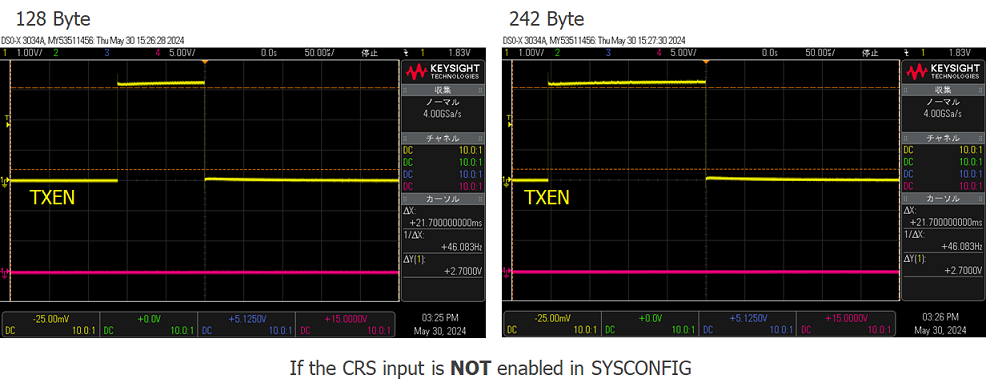

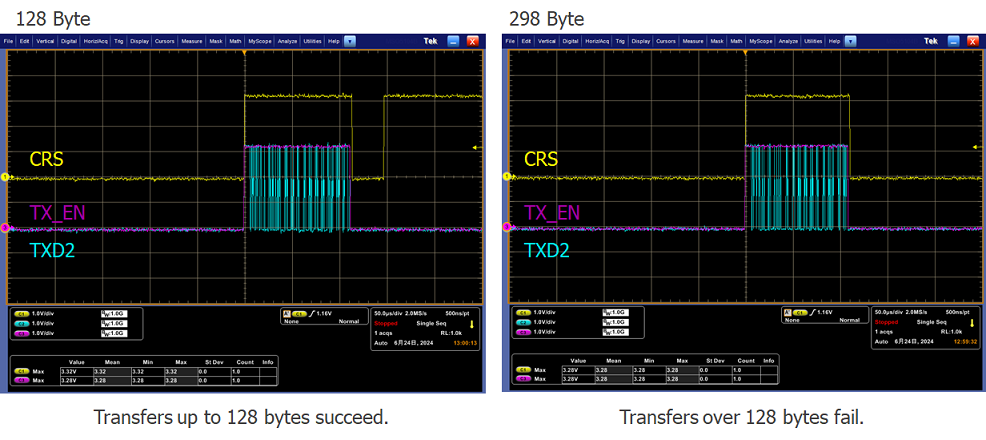

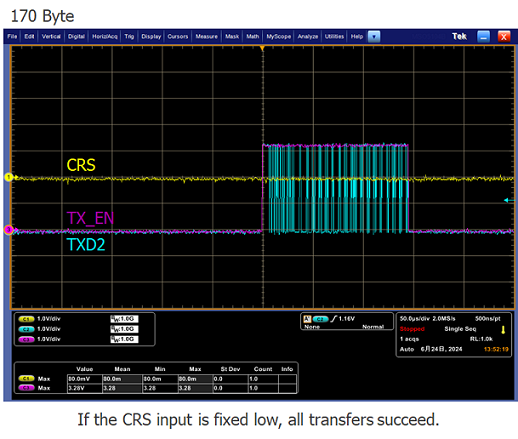

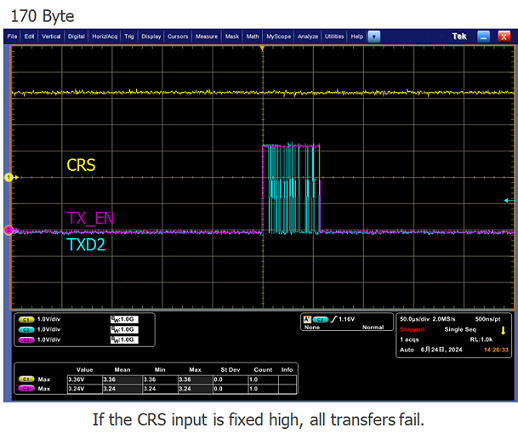

They are testing between two AM2434 prototype boards, but a frame length is limited to 128 bytes when the CRS input is enabled.

Best regards,

Daisuke