Part Number: MSPM0G3507

Tool/software:

Hello,

I am trying to find an example for SPI communication. Only found bsl_spi_flash_interface, in which the SPI is configured as a peripheral instead of controller.

Is there any example for SPI as a controller?

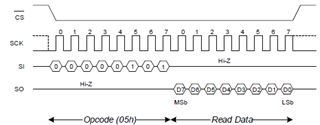

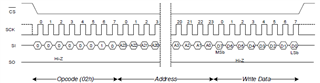

Eventually my question is this. When the MCU is a SPI controller, how will the clock for the slave to respond generated?

In the driverlib API for receiving data from the slave, it doesn't send dummy data to generate the clock.

__STATIC_INLINE uint8_t DL_SPI_receiveData8(SPI_Regs *spi)

{

return ((uint8_t)(spi->RXDATA));

}