Tool/software:

HI:

we use the demo project of mibspi_loopback_dma_am273x-evm_r5fss0-0_freertos_ti-arm-clang to cfg the TJA1145 cantrancv.

comment the code status = MIBSPI_enableLoopback(gMibspiHandle[CONFIG_MIBSPI0],loopback); to disable loopback function

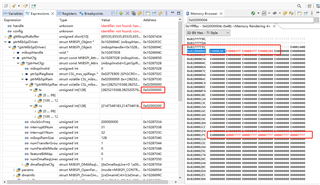

and we find the TX and RX data right on the spi miso and mosi bus.but err in RXSRAM.

Another experiment do not comment the code status = MIBSPI_enableLoopback(gMibspiHandle[CONFIG_MIBSPI0],loopback); enable loopback function,the RXSRAM data is right.

in addition ,the e2e case about pmic I request before. use the same demo project and the spi used as mibspib, it's useful.

chang the Macro definitions and variables as follows:

#define APP_MIBSPI_MSGSIZE 10

uint16_t gMibspiTxBuffer1[APP_MIBSPI_MSGSIZE];

uint16_t gMibspiRxBuffer[APP_MIBSPI_MSGSIZE];

uint16_t gMibspiTxBuffer[]=

{

// 0x03ff, // Reg 1 Mode control

0x1400, // Reg:0x0A Lock control. Spi write access enable

0x0207, // Reg 1 Mode control

0x03ff, // Reg 1 Mode control

0x03ff, // Reg 1 Mode control

0x0204, // Reg 1 Mode control

0x03ff, // Reg 1 Mode control

0x03ff, // Reg 1 Mode control

0x0207, // Reg 1 Mode control

0x03ff, // Reg 1 Mode control

0x03ff, // Reg 1 Mode control

};

memory:

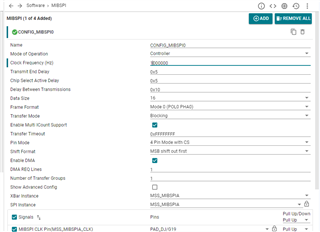

syscfg :

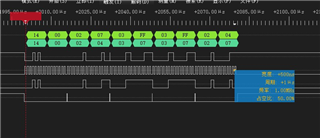

spi bus:

3Q.