Tool/software:

Hi expert,

I'm lookin for some missing registers information in TRM in order to use ESM module.

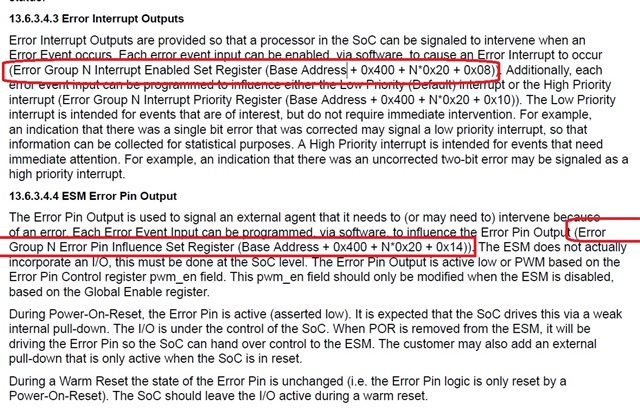

In TRM, it mentions Error Group N Interrupt Enabled Set Register ...

But there is nothing useful information in AM263x Register Addendum. Table 4-4287. TOP_ESM Registers Base Address Table even didn't list registers offset 0x400 and above and what they mean.

I also looking for e2e but looks others also feel confusing and did not get answer.

When I look into demo project and source code, I feel more confusing. Especially .esmErrorConfig.

#if defined (SOC_AM263X) || defined (SOC_AM263PX)

SDL_ESM_config DCC_Test_esmInitConfig_MAIN =

{

.esmErrorConfig = {1u, 8u}, /* Self test error config */

.enableBitmap = {0x01E00000u, 0x00000000u, 0x00000000, 0x00000000u,

},

/**< Only DCC events enable:**/

/* CCM_1_SELFTEST_ERR and _R5FSS1_COMPARE_ERR_PULSE_0 */

.priorityBitmap = {0x01E00000u, 0x00000000u, 0x00000000, 0x00000000u,

},

/**< DCC events high priority:**/

.errorpinBitmap = {0x01E00000u, 0x00000000u, 0x00000000, 0x00000000u,

},

/**< All events high priority:**/

};

sdlr_esm.h

#define SDL_ESM_ERR_GRP_RAW(ERR_GRP) (0x00000400U+((ERR_GRP)*0x20U))

#define SDL_ESM_ERR_GRP_STS(ERR_GRP) (0x00000404U+((ERR_GRP)*0x20U))

#define SDL_ESM_ERR_GRP_INTR_EN_SET(ERR_GRP) (0x00000408U+((ERR_GRP)*0x20U))

#define SDL_ESM_ERR_GRP_INTR_EN_CLR(ERR_GRP) (0x0000040CU+((ERR_GRP)*0x20U))

#define SDL_ESM_ERR_GRP_INT_PRIO(ERR_GRP) (0x00000410U+((ERR_GRP)*0x20U))

#define SDL_ESM_ERR_GRP_PIN_EN_SET(ERR_GRP) (0x00000414U+((ERR_GRP)*0x20U))

#define SDL_ESM_ERR_GRP_PIN_EN_CLR(ERR_GRP) (0x00000418U+((ERR_GRP)*0x20U))

Can you please provide more detail information about our ESM? Without detail, we don't know how to guide customer to use our ESM feature.

When will we provide updated TRM? Thanks.

Regards

Andre