Other Parts Discussed in Thread: SYSCONFIG

Tool/software:

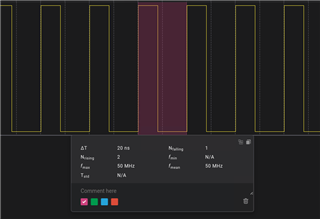

For a custom PCB that includes multiple DP83826 PHYs I would like to use that AM263Px.CLKOUT0 pin as the DP83826.XI (clock input).

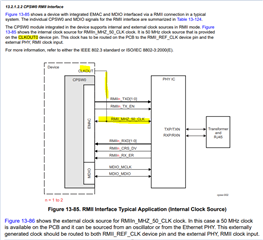

DP83826 Datasheet Excerpt1:

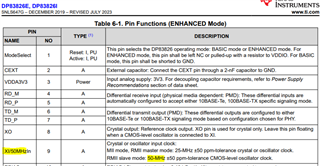

DP83826 Datasheet Excerpt2

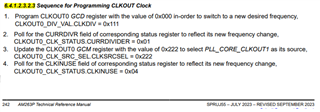

However, it is not clear how I can configure AM263Px.CLKOUT0 to output the 50MHz clock needed.

a)

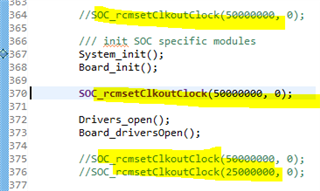

It seems like there may be a way to configure this through SysConfig through:

{BUILD_CONFIG_OUTPUT_PATH}/syscfg/ti_power_clock_config.c

However, I do not see where in the GUI to configure this.

Is it possible to configure the clock through SysConfig?

b)

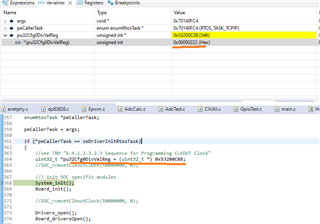

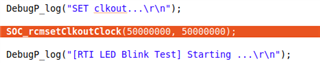

Or can it by done through a driver API call? is this API call what I’m looking for?

void SOC_rcmCoreApllHSDivConfig(SOC_RcmPllFoutFreqId outFreqId, SOC_RcmPllHsDivOutConfig *hsDivCfg)

… defined here:

${COM_TI_MCU_PLUS_SDK_AM263PX_INSTALL_DIR}\source\drivers\soc\am263px\soc_rcm.c

c)

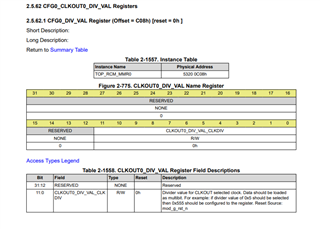

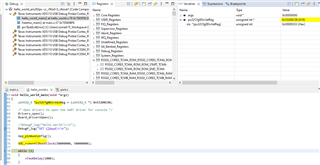

I also see what looks like the register addresses that may control CLKOUT0 in file:

${COM_TI_MCU_PLUS_SDK_AM263PX_INSTALL_DIR}\\source\drivers\hw_include\am263px\cslr_iomux.h

.. sections:

/* CLKOUT0_CFG_REG */

/* PLL_PER_HSDIVIDER_CLKOUT0 */

Is using direct register writes an option?

Please advise.