Tool/software:

Hi,

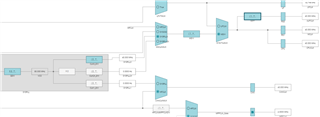

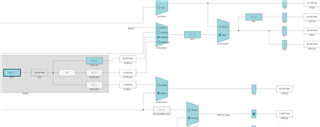

When I was using the ADC to collect values, something happened: When Sample Clock Divider = 1 or 2, everything looked normal. But when Sample Clock Divider = 24, I received some noise, and the normal picture was The abnormal picture is below. There is an interesting thing at the same time. If I reduce the CPUCLK to 40M, no matter what the Sample Clock Divider is, it will be normal. What is the reason? How can I take into account both CPUCLK = 80M and Sample Clock Divider = 24? ? The ADC Clock Source is ULPCLK

Thanks for your help