Other Parts Discussed in Thread: AM6421, SYSCONFIG

Tool/software:

Hello,

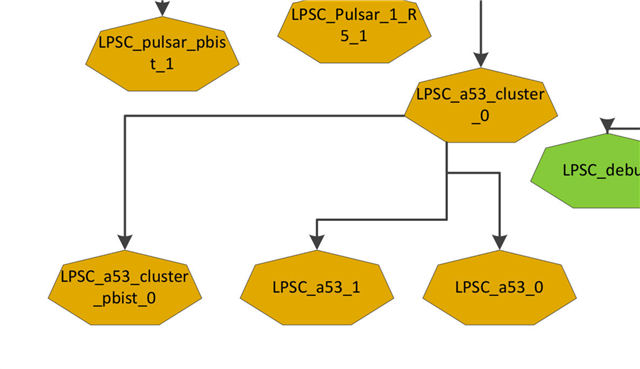

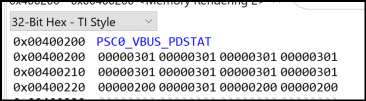

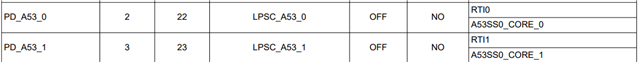

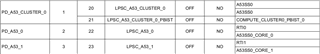

I'm currently using the AM6421 with the R5s running RTOS only. When I check the PSC state of the A53 Cluster and Core0, the status returns that they are enabled. I'm trying to determine the appropriate way to disable the LPSCs and PLLs, and HSDIVs associated with the A53 and other unused subsystems.

In the MCU Plus SDK, I see in soc.c: SOC_get and _setPSCState. This appears to be the way to shut power off on the A53 and other LPSCs. However, the only example of get/set PSC's use is found in reset_isolation_ipc_mcu_domain. Not sure if it's a valid approach to follow for the A53.

I'm also trying to understand how the DMSC and TISCI fits into this with regard to disabling LPSCs, PLLs, HSDIVs. Can you point me to specific examples of how these are shutdown from the RTOS application?

Thank you,

Joe