Other Parts Discussed in Thread: SYSCONFIG, DP83869, LP-AM243, UNIFLASH

Tool/software:

Hi TI Experts,

We are discussing offline about the support of ethernet primary boot & backup boot. As following your suggestion, I also created E2E thread here to involve customer together so that we could stay on the same page.

In the last email thread, customer followed the below steps to see if the ethernet backup boot is working properly on their board.

- Power off the board

- Switch the boot mode to UART primary and Ethernet backup mode.

- Connect an ethernet cable from the board’s Ethernet port to a PC port.

- Start monitoring the PC port connected to the board using Wireshark.

- Power on the board.

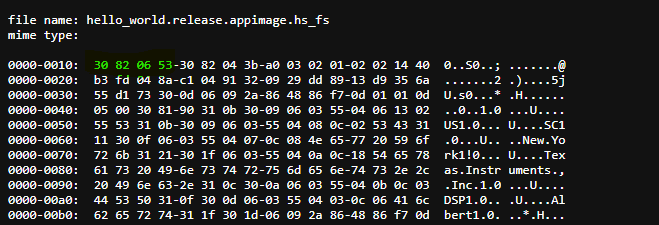

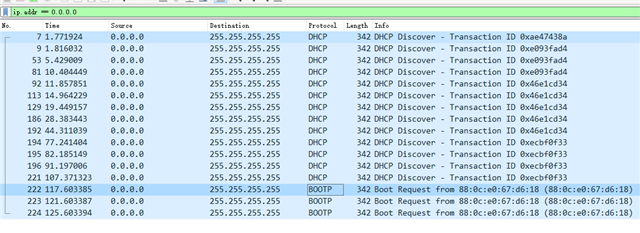

Customer got the Wireshark screenshot below.

Customer is pretty sure the MAC address 88:0C:E0:67:D6:18 is for the AM2431 on their board, since the Ethernet port of the board is directly connected to their computer’s Ethernet port with a cable, and their computer’s MAC is totally different.

By the way, customer notices that for the backup boot, AM2431 only sends BOOTP request about 117s after power up. It is a little bit too long.

If Ethernet Boot program/tools is ready, customer will change the Ethernet as Primary boot (with mode change switch) in next board spin.

So please make sure the Ethernet boot tool we are working on can work for both Primary boot as well as backup boot.

Thanks,

Kevin