Other Parts Discussed in Thread: TM4C123GH6PM, , EK-TM4C1294XL

Tool/software:

We have a design that was previously implemented using a TM4C123GH6PM, which we are now migrating to a TM4C1290NCPDT.

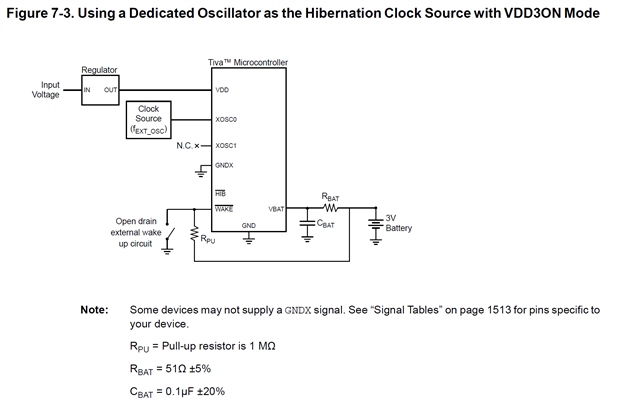

In our system, the hibernation module powers the circuit off by disabling regulators using its /HIB output. The code instructs the system to hibernate on command, and it can be woken by timer or /WAKE pin. /WAKE is pulled up to the coin cell that powers the hibernation module (VBAT) by a 1M pullup. I know this is a very weak pullup, but we are doing very low power operations and trying to save battery. The system also wakes on serial Rx because /WAKE is pulled to ground by a mosfet circuit with Rx on the gate.

The following screenshot shows expected behavior, using the TM4C123GH6PM. Ch1 (yellow) = VBAT (coin cell), Ch2 (blue) = /WAKE, Ch3 (pink) = /HIB, Ch4 (green) = 3.3V main power to processor.

Since /WAKE is tied to Rx, the command to hibernate can be seen in the /WAKE line. Around 250ms later, /HIB goes low, then main power goes away as the regulator is disabled.

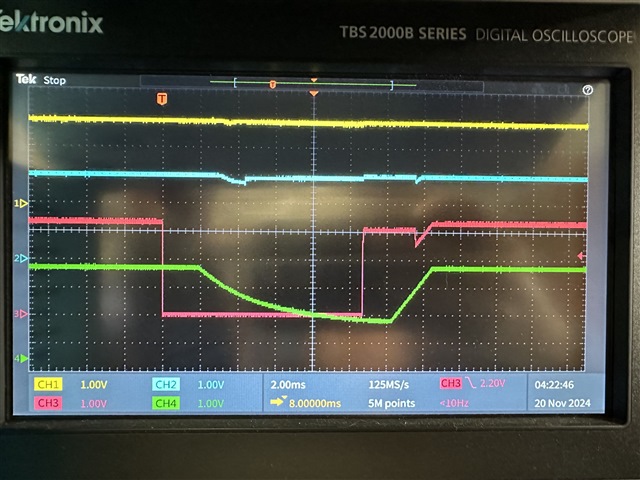

On the TM4C1290, the same behavior looks like:

The system wakes up immediately after it goes to sleep.

Zooming in on the behavior around when /HIB goes low (to turn off the regulator),

It seems like the /WAKE line is sagging. I wonder if somewhere internally on the TM4C129, /WAKE is affected by the main power, since I know there were some changes in behavior surrounding the main power takeover of the Hibernation module while awake.

Even though it's not ideal for our current consumption, I strengthened the pullups on /WAKE line. Using a 10k pullup instead of 1M, I got the following waveform:

(I also got some different strange behavior using a 100k pullup, but the above waveform more clearly indicates that sag on the /WAKE pin is probably not what's causing the system to wake up.)

I do have a version of this circuit where the regulator is not disabled by /HIB, so main power stays present even after the system hibernates. It's also different in a few other ways (eg no wake on Rx). This version hibernates properly and there is no sag on /WAKE, even with the 1M pullup. However, none of the ways it's different stand out to me as something that could make the difference. The idea of /WAKE sagging below threshold due to being affected by main power seems to be disproved by the above scope trace (also, it never even got that low).

I'm looking for ideas on what might be causing our system to wake up immediately after hibernation. I'm not sure if the behavior of the /WAKE line is a clue or not, but I would prefer to use the weakest pullups I can to save power. The circuitry and code around the hibernation module should be pretty much the same as the working TM4C123 board. I looked through some of the differences between the TM4C123 and TM4C129, and while I do, e.g. ground some of the GPIOs that can be configured to Wake, they should not be configured in the software to function as /WAKE.

Thanks!