Part Number: AM263P4-Q1

Other Parts Discussed in Thread: UNIFLASH, AM263P4, SYSCONFIG

Tool/software:

Hi

I'm using CCS theia version 1.5.1.3.

Using the AM263P launchpad, I'm trying to get a simple application running in XIP but I can't seem to be able to.

I followed the threads about this:

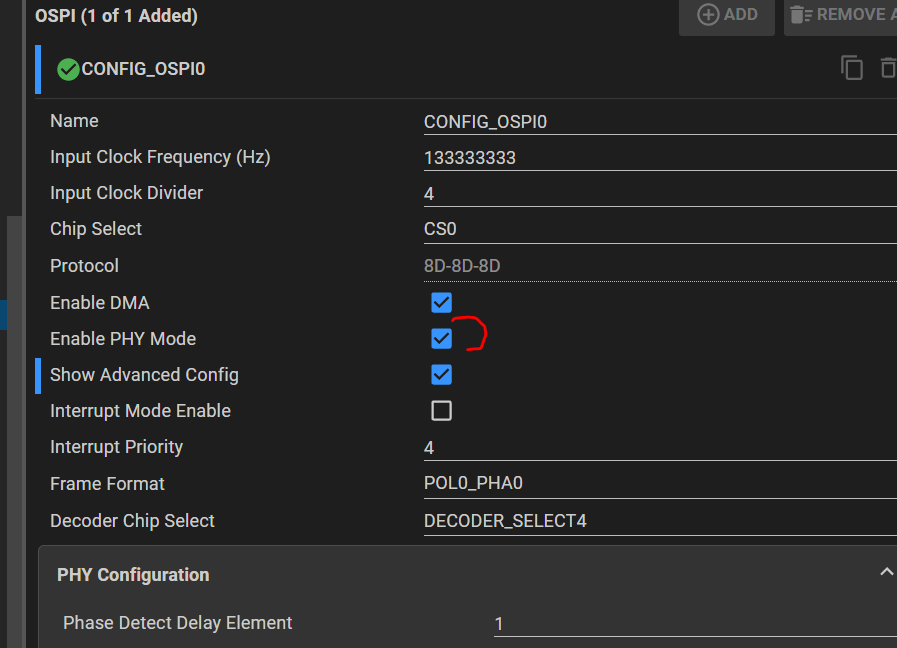

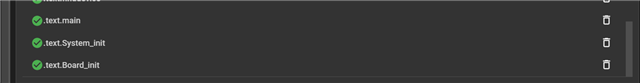

My SysCfg setup is therefore looking like this:

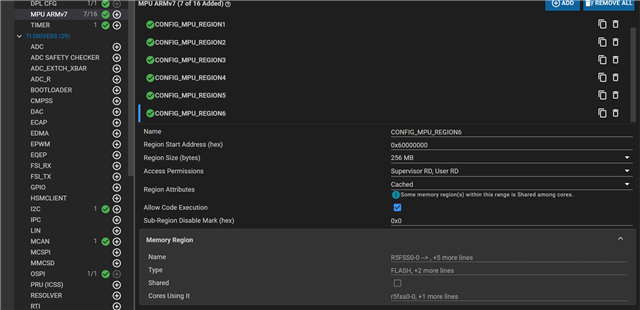

MPU setup :

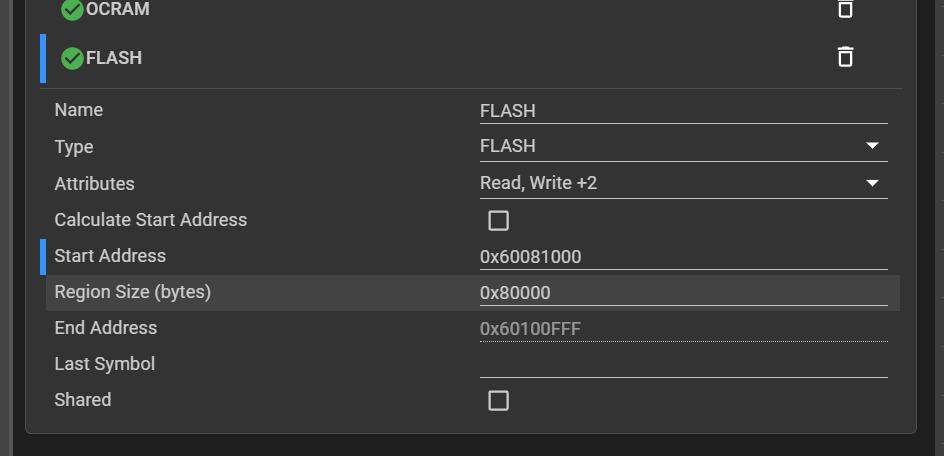

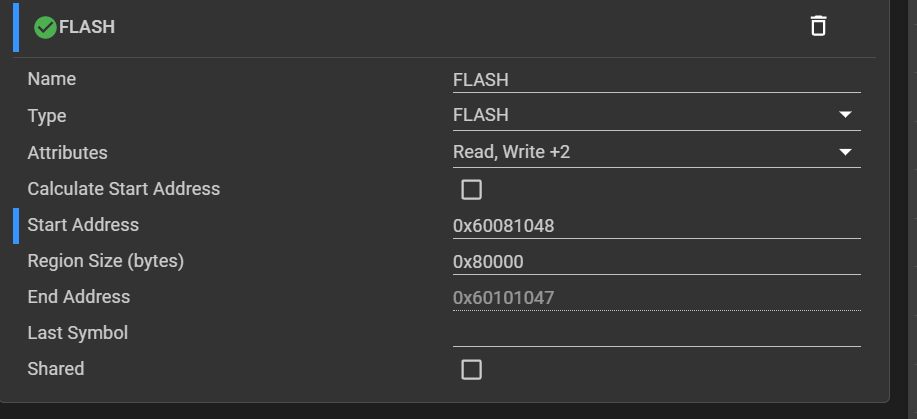

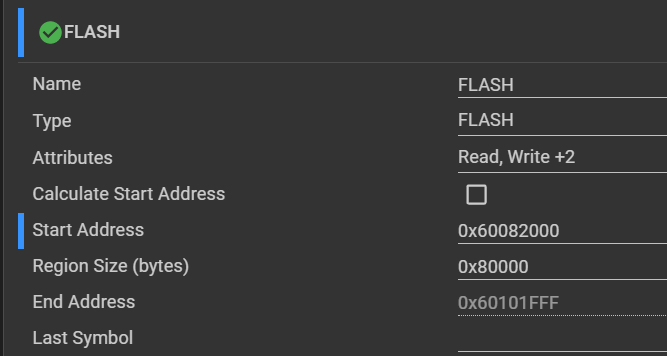

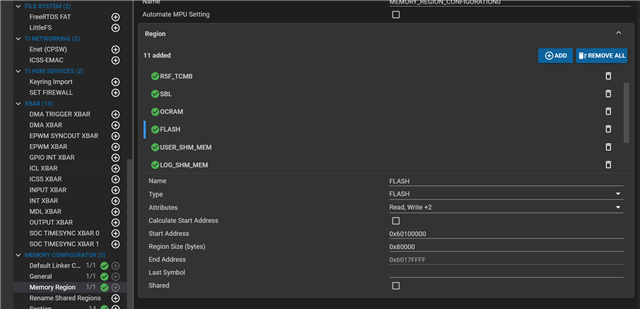

In the memory regions, I have the flash set up like this:

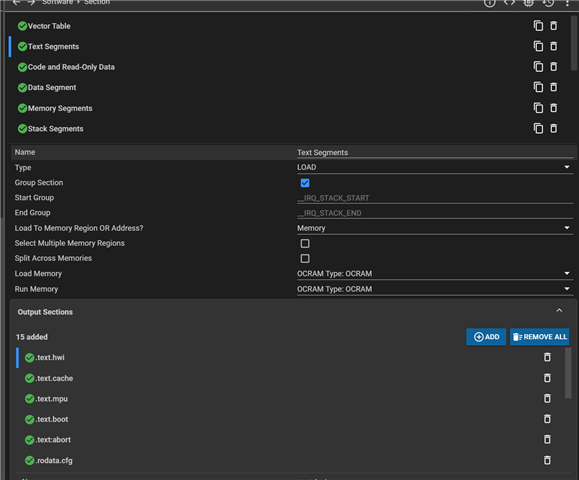

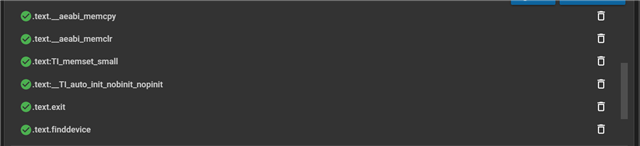

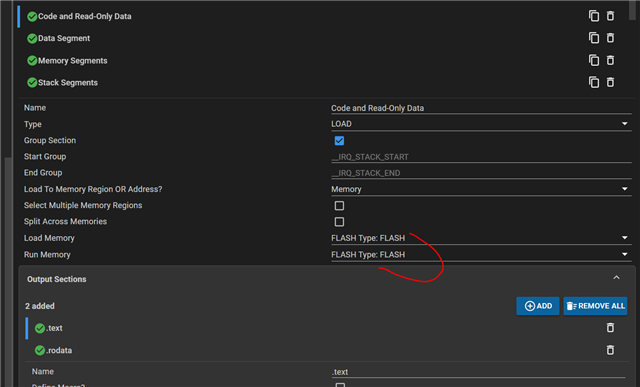

Then in sections I have:

Adding all the sections below .rodata.cfg in OCRAM allowed the code to execute until main and the while loop introduced at the start.

Otherwise, the code would go into a prefetch abort in _system_pre_init and __TI_auto_init in the startup code from reset to main.

Then I have the rest of the code in FLASH like suggested into the threads above:

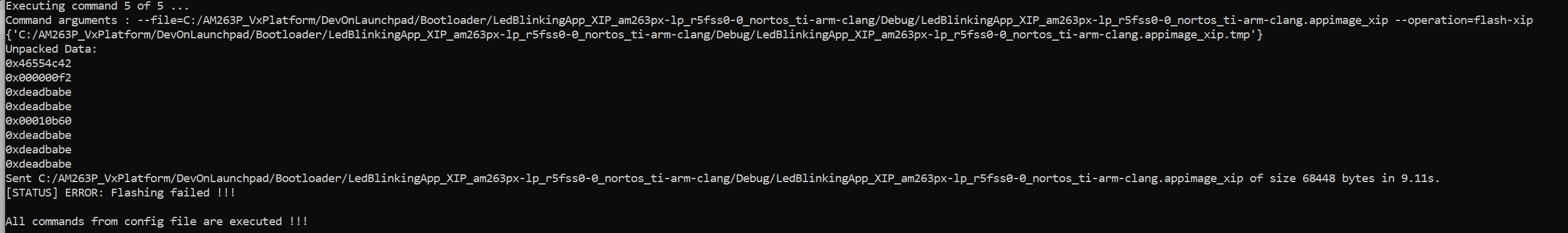

When flashing I put the launchpad board in uart boot mode and flash using the uart_uniflash python script called from a command line:

python uart_uniflash.py -p COM11 --cfg=C:/ti/mcu_plus_sdk_am263px_10_00_00_35/tools/boot/sbl_prebuilt/am263px-lp/default_sbl_ospi_Seb.cfg

My config file is looking like:

# First point to sbl_uart_uniflash binary, which function's as a server to flash one or more files

--flash-writer=sbl_prebuilt/am263px-lp/sbl_uart_uniflash.release.tiimage

# Program the OSPI PHY tuning attack vector

--operation=flash-phy-tuning-data

# When sending bootloader make sure to flash at offset 0x0. ROM expects bootloader at offset 0x0

--file=sbl_prebuilt/am263px-lp/sbl_ospi.release.tiimage --operation=flash --flash-offset=0x0

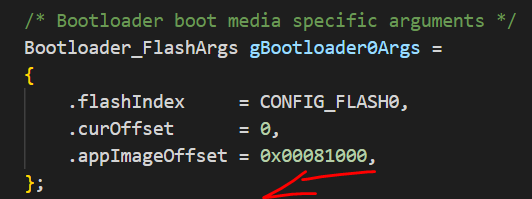

# When sending application image, make sure to flash at offset 0x81000 (default) or to whatever offset your bootloader is configured for

#--file=../../examples/drivers/ipc/ipc_notify_echo/am263px-lp/system_freertos_nortos/ipc_notify_echo_system.release.appimage --operation=flash --flash-offset=0x81000

#--file=C:/AM263P_VxPlatform/DevOnLaunchpad/Bootloader/LedBlinkingApp_am263px-lp_r5fss0-0_nortos_ti-arm-clang/Debug/LedBlinkingApp_am263px-lp_r5fss0-0_nortos_ti-arm-clang.appimage --operation=flash --flash-offset=0x81000

--file=C:/AM263P_VxPlatform/DevOnLaunchpad/Bootloader/LedBlinkingApp_XIP_am263px-lp_r5fss0-0_nortos_ti-arm-clang/Debug/LedBlinkingApp_XIP_am263px-lp_r5fss0-0_nortos_ti-arm-clang.appimage --operation=flash --flash-offset=0x81000

#XIP section

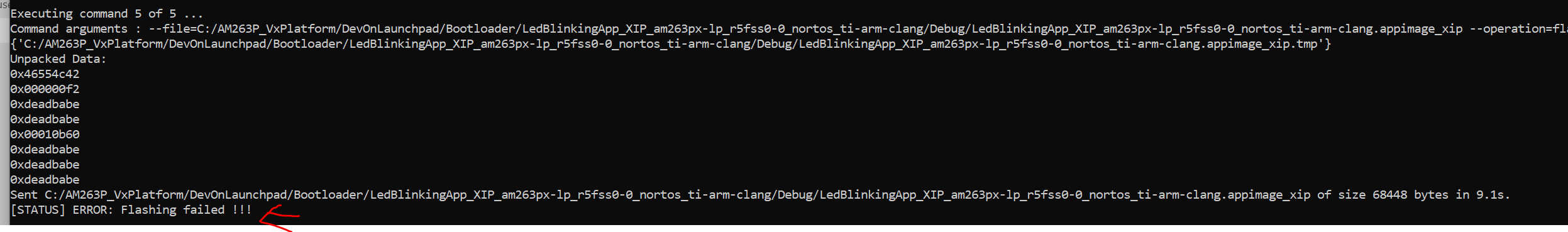

--file=C:/AM263P_VxPlatform/DevOnLaunchpad/Bootloader/LedBlinkingApp_XIP_am263px-lp_r5fss0-0_nortos_ti-arm-clang/Debug/LedBlinkingApp_XIP_am263px-lp_r5fss0-0_nortos_ti-arm-clang.appimage_xip --operation=flash-xip

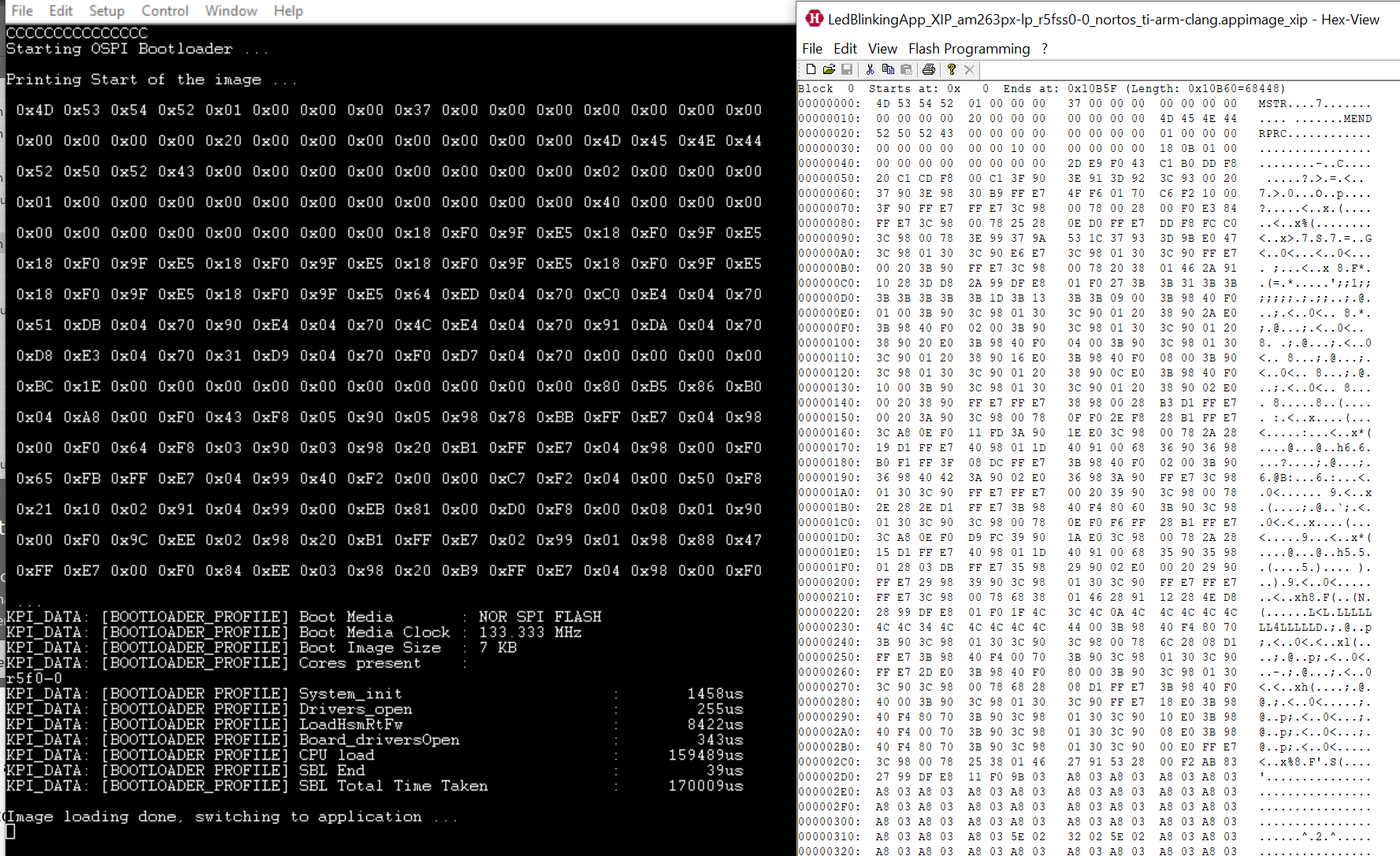

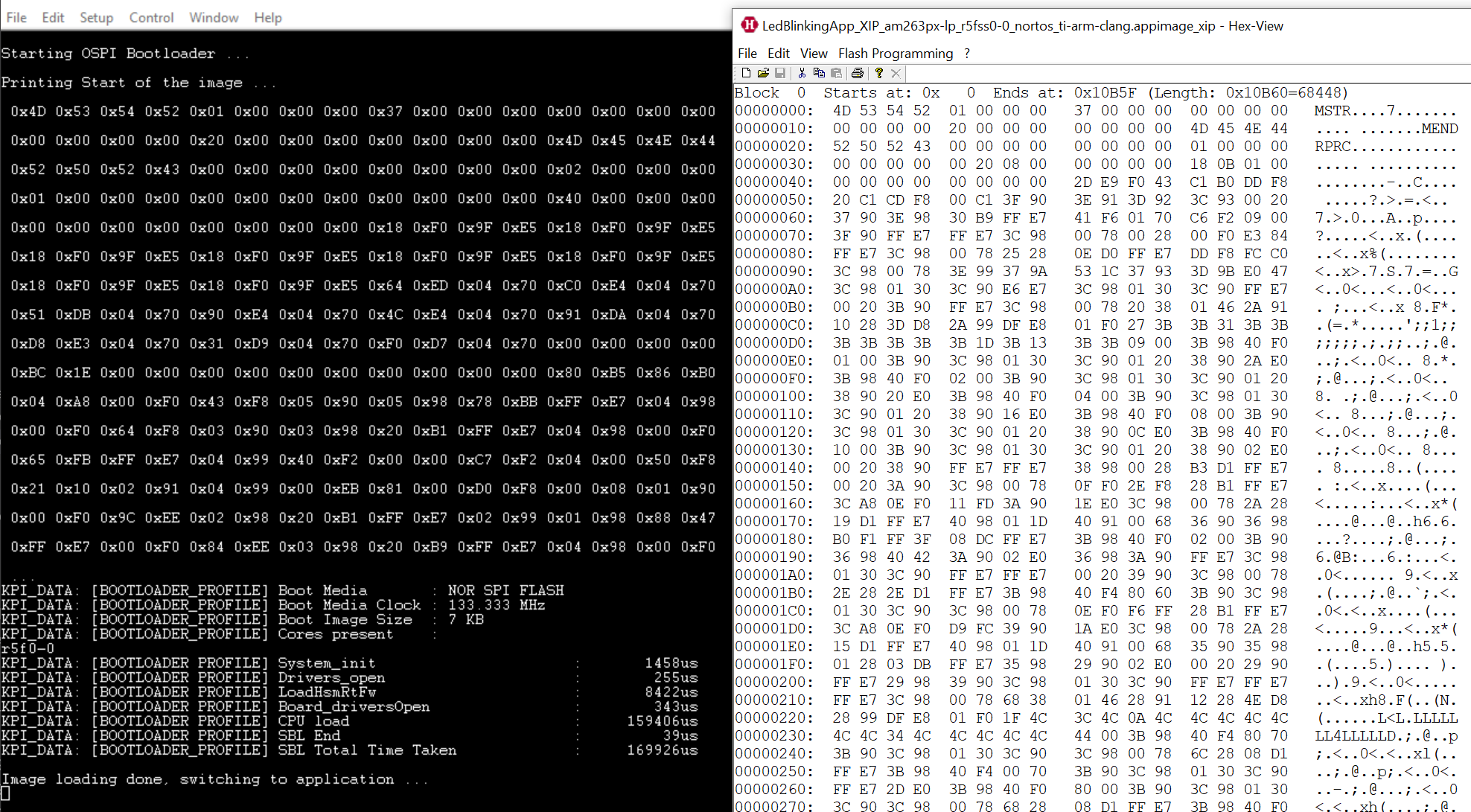

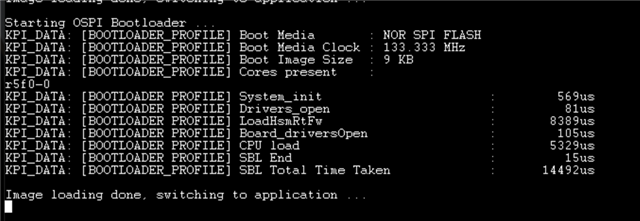

The flashing works OK, and I can see the following output from SBL:

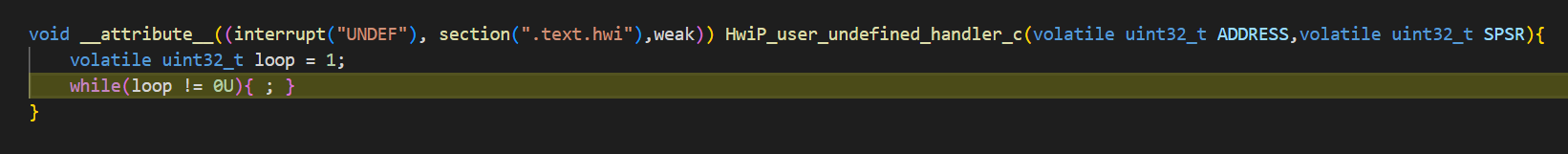

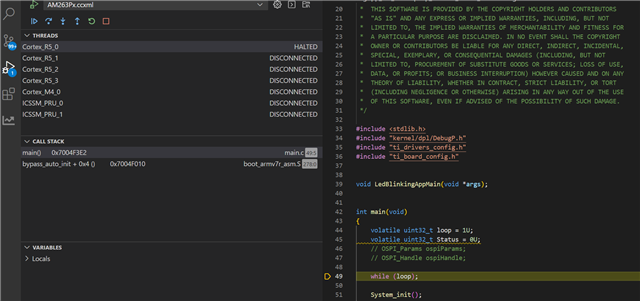

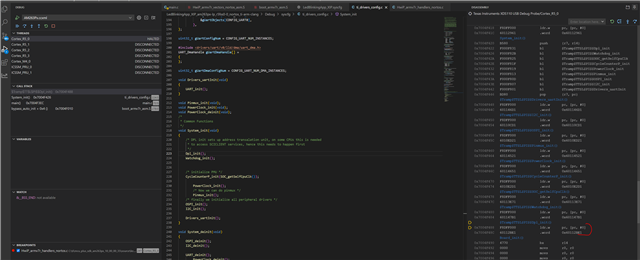

When debugging the application, I'm getting into the waiting loop at the start of the main function as expected:

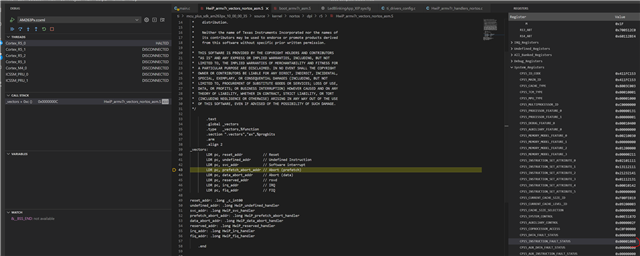

When stepping through the code, the execution goes well until a trampoline to execute from flash which causes a prefetch abort again:

I believe I followed all the steps indicated in the developer training for AM263P4.

I must miss something or do something wrong. Given the exception it is looking like the CPU does not have visibility on the external flash memory.

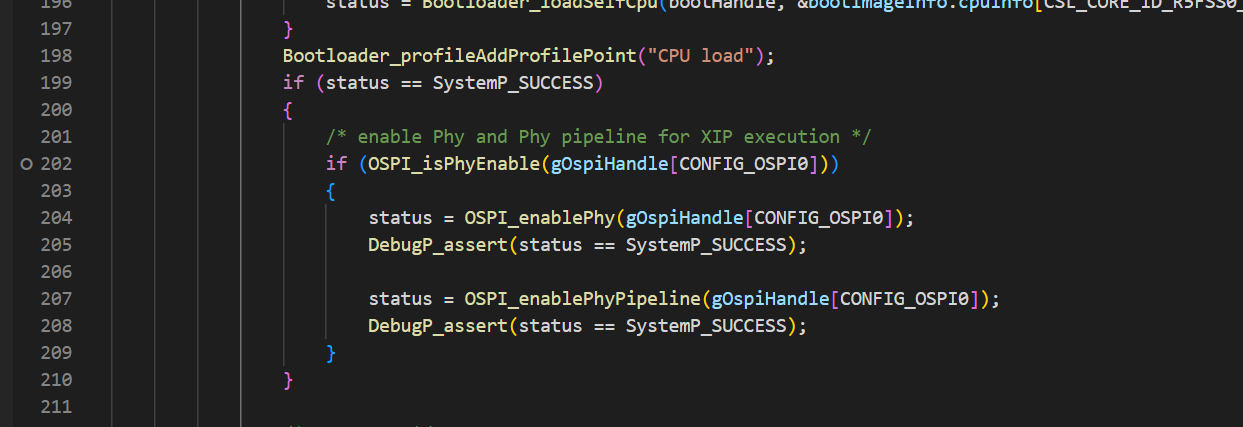

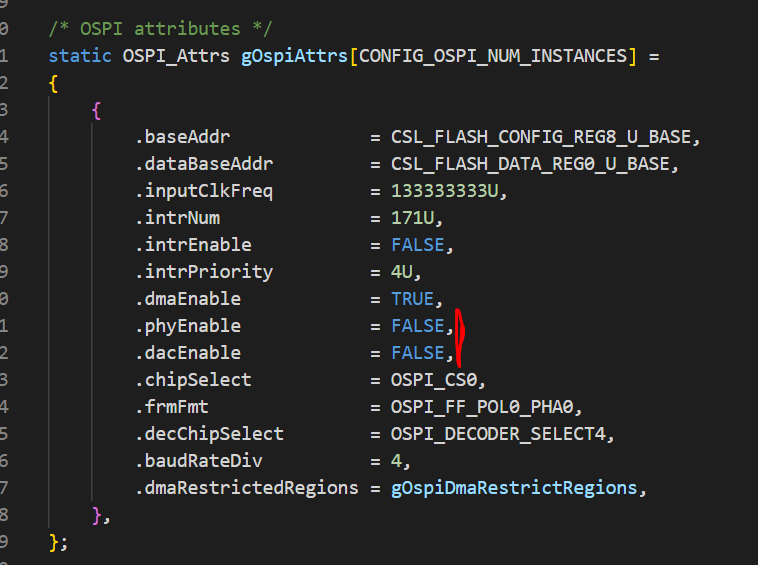

Following on the documentation below, I'm expecting the SBL to set the FLASH memory right to support XIP and especially activate DAC mode:

From the documentation it looks like it is straight foward but it actually is not. Would it be possible to point me into what I'm doing wrong and point me into the right direction ?

Happy to share the project if required.

Thanks

Regards

Seb