Tool/software:

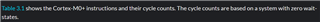

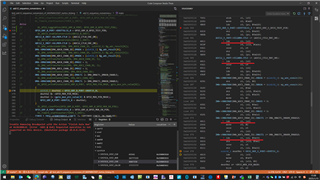

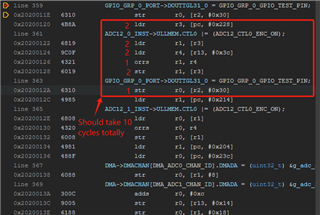

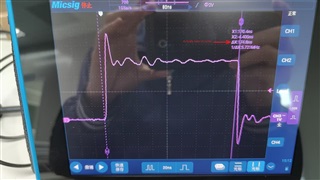

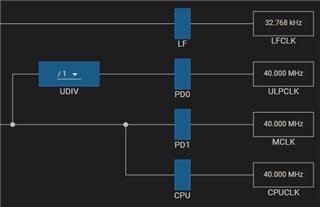

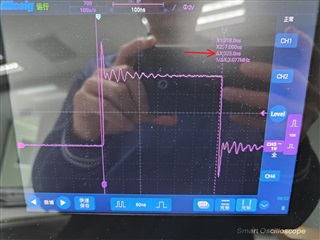

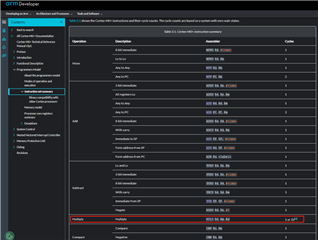

For example, we can see that CPU executes the instruction MULS by taking 4 clock cycles. However, the information came from ARM's web site shows that it takes 1 or 32 clock cycles. Please help comfirm.

https://developer.arm.com/documentation/ddi0484/c/Programmers-Model/Instruction-set-summary