Part Number: TMDSCNCD263P

Other Parts Discussed in Thread: TCA6424, TCA6416, UNIFLASH

Tool/software:

Hello,

I am trying to get the TI example for OSPI communication working. There seems to be an issue with the OSPI driver setup in the flash_diag example.

The aim is to get the example with XIP (benchmarks/ocmc) working, but I was having issues with this. As such, I switched to ensuring OSPI flash communication works as intended.

Hardware: TMDSCNCD263P, ControlCard version PROC159A

SDK version: mcu_plus_sdk_am263px_10_01_00_31

Steps done so far:

1. Run ospi_flash_diag example (C:\xx\mcu_plus_sdk_am263px_10_01_00_31\examples\drivers\ospi\ospi_flash_diag\am263px-cc\r5fss0-0_nortos) without bootloader (DEV_BOOT mode). Result: This runs OK, I can see same UART output as example.

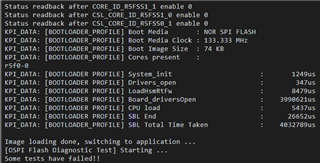

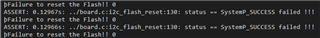

2. Run ospi_flash_diag example with sbl_ospi.release.tiimage under "C:\ti\mcu_plus_sdk_am263px_10_01_00_31\tools\boot\sbl_prebuilt\am263px-cc\". Flash sbl_ospi with offset 0x0 and ospi_flash_diag with offset 0x81000 as intended. Result:

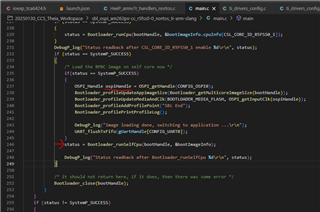

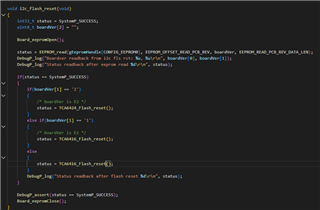

3. Debugged bootloader in i2c_flash_reset, with code below. Debug output from the EEPROM read returns 0, and so the default function goes into TCA6416_Flash_reset, which is incorrect as that chip was only present on the earlier version of the ControlCard (version PROC159E2). There's a question why the EEPROM does not return the correct value for boardver (0), but this this code probably needs updating so the default function is TCA6424_Flash_reset.

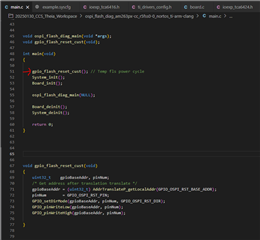

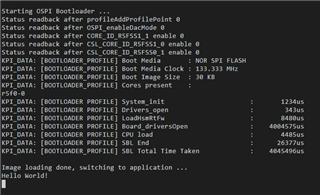

4. Created custom bootloader with this step from #3 above. Flash this using UniFlash together with helloWorld application. Run application from OSPI. Result: serial output is OK. (so custom bootloader is OK, OSPI load from boot seems to work also)

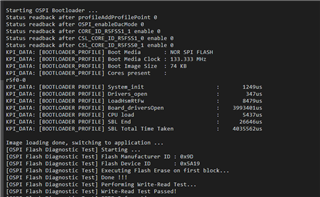

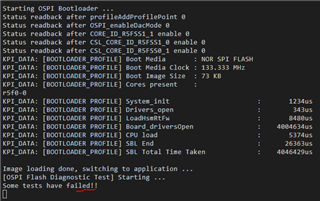

5. Flash custom bootloader and ospi_flash_diag example from #1. Now, we get one step further as we enter application, but fail on the first step of communicating with the flash chip from there.

This implies we fail on execution of the first OSPI_norFlashReadId(). I have not continued debugging but it would seem like there is something fundamentally wrong with OSPI modes/sequencing or similar. Could a member of TI go through this last step and verify the OSPI SBL works OK with the Flash Diag example?

Thanks,

Rens