Part Number: AM2434

Other Parts Discussed in Thread: LP-AM243

Tool/software:

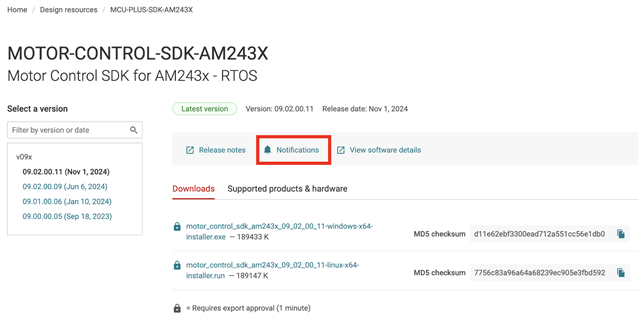

Subject: motor control sdk 9.2.0.9

Hi there,

in previous post I know how sync0 and sync1 signals are exposed on some pins on LP-AM243 board. I have more questions.

Can one also get PDI events on an external pin on SOC?

In addition, I see Sync0_Isr(), Sync1_Isr(), EcatIsr() among others in tiescbsp.c and macros in tiescbsp.h (ENABLE_SYNC_TASK and ENABLE_PDI_TASK).

Are Sync0, Sync1 and PDI interrupts enabled by default? If yes, the default ISRs will just clear the interrupt status bits by default, right?

Best regards,

Jinlong

Reference:

dev.ti.com/.../ETHERCAT_SUBDEVICE_FWHAL.html