Tool/software:

Hey.

I am working setting up some center aligned pwm signals, and are setting it up for using the shadow compare feature, to only update the compare value on a ZERO event.

It works fine, but there is one oddity:

The very first duty cycle seems to have an arbitrary length that I cannot seem to change. After the first pulse, things work fine, but no matter which order I write the registers, the first pulse seem unaffected.

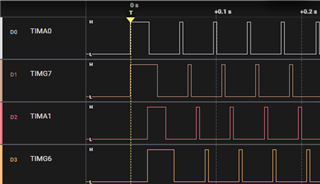

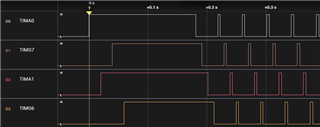

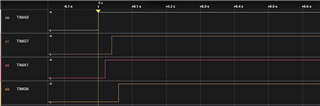

Here's a screenshot with an initial duty cycle set up for 10% showing the issue: