Tool/software:

When I use PRU to read out the memory date , LBBO command cost 120ns, it is too long.

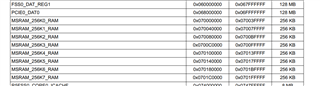

I need my logic to work at a 100ns clock frequency. In each cycle, I need to read data from memory, but LBBO command takes nearly 120ns, which is abnormal. When I use the LBCO command, it only takes 15ns. I think this might be related to the memory address. I'm using the 0x70000000 MSRAM area, writing from R5, and reading via PRU. 120ns seems too long. Is there a way to shorten the time of this command? My PRU works at 200Mhz, with a single - instruction - cycle time of 5ns.

Code:

LBBO &PIXEL_DATA, SHARED_MEM, 0, 2 ; cost 120ns

MOV r30.w0, PIXEL_DATA