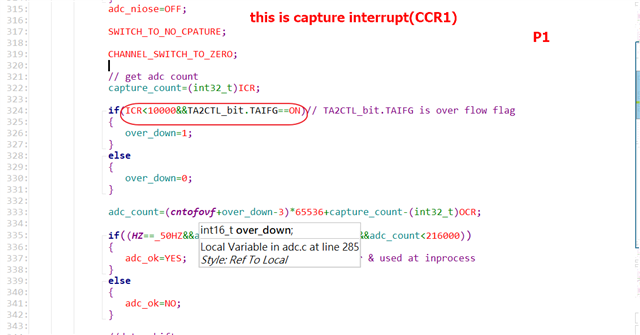

Part Number: MSPM0G3507

Other Parts Discussed in Thread: MSP430F5324,

Tool/software:

Hi expert

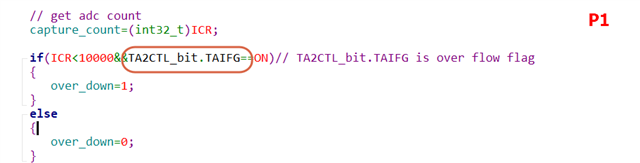

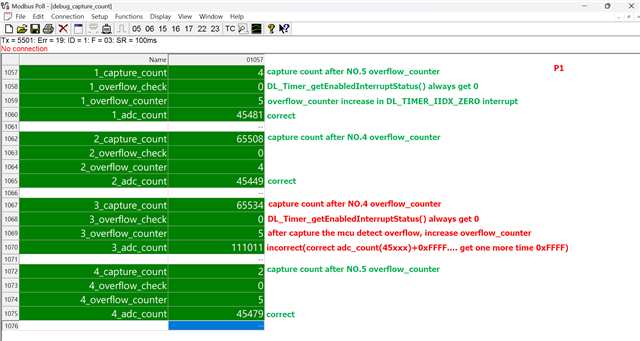

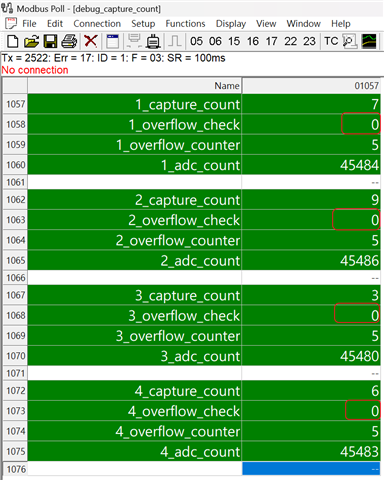

in my previous project(MSP430F5324), i use TAIFG bit to detect timer overflow(P1),

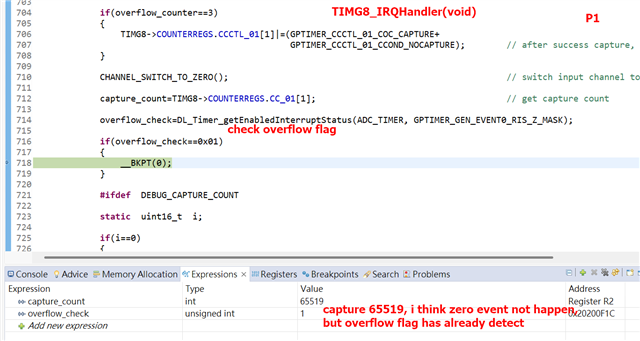

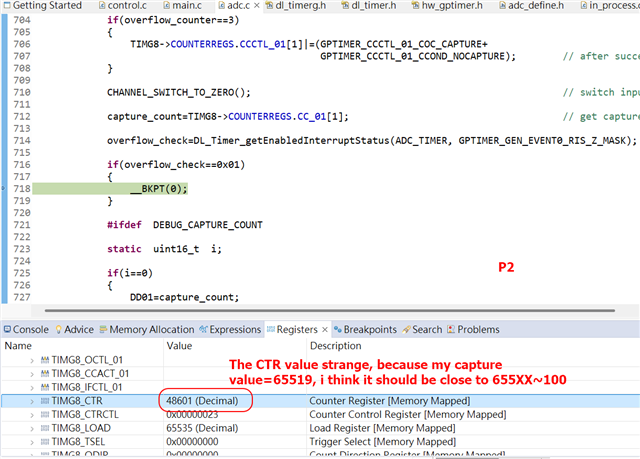

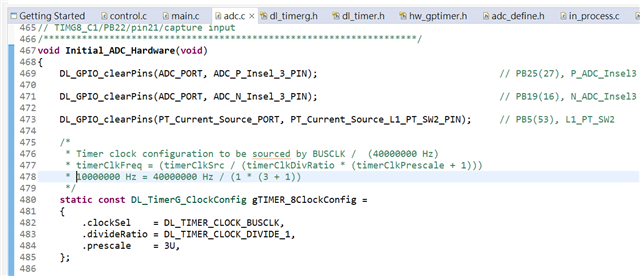

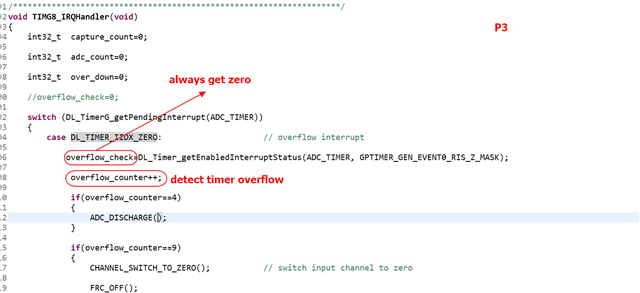

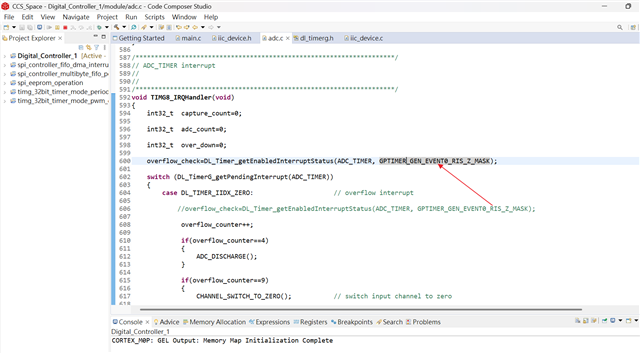

now in current project(MSPM0G3507) which register can meet my need?

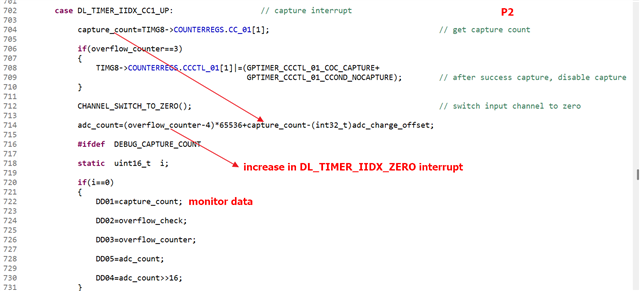

Is TOV bit(P2) available?