Other Parts Discussed in Thread: SYSCONFIG, AM2634, AM263P4, UNIFLASH

Tool/software:

Hello,

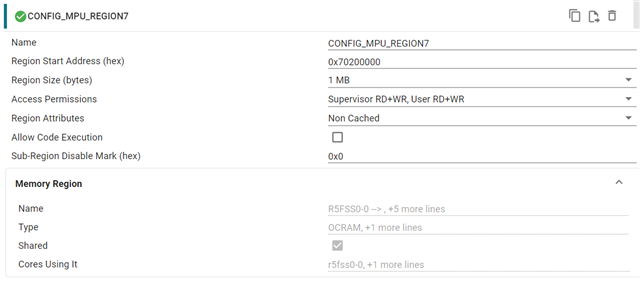

I'm trying to use the memory region from 0x7020 0000 to 0x702F FFFF as shared memory. As none of the examples define this region in the MPU, I added an entry in the sysconfig as below:

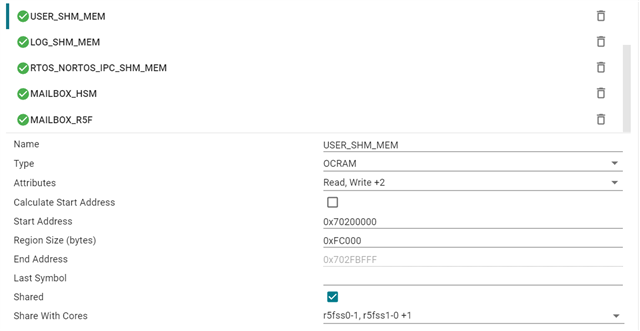

and then in the memory regions, set it as shared:

In the code, I have a variable defined as follows:

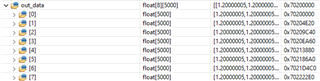

#define OUTPUT_BUFFER_LENGTH 5000

#define ANALOG_CHANNELS_PER_CORE 4volatile float out_data[ANALOG_CHANNELS_PER_CORE * 2][OUTPUT_BUFFER_LENGTH]__attribute__((section(".bss.user_shared_mem")));

and then I tried to initialize the array to 0:

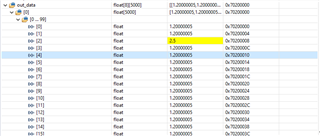

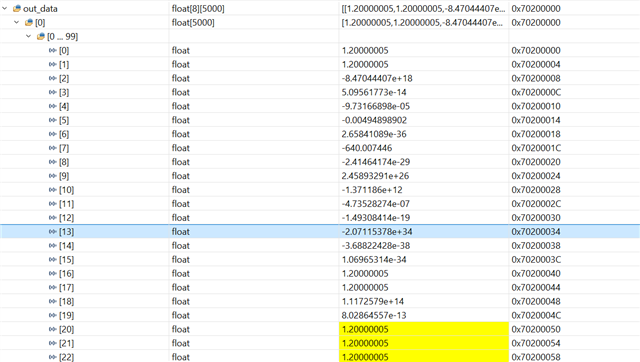

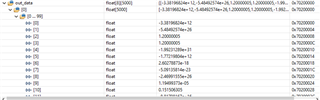

for(uint16_t i = 0; i < (ANALOG_CHANNELS_PER_CORE * 2); i++) { for(uint16_t j = 0; j < OUTPUT_BUFFER_LENGTH; j++) { out_data[i][j] = 0.0f; } }

The problem is not all values get sets to 0, if I pause the application and try to manually set the array values to 0, it still doesn't work! I wonder if that is a silicon issue? do I have a bad SOC? or a configuration issue?

Update: I tested another board and got the same result, so it isn't a bad SOC.