Part Number: AM2432

Other Parts Discussed in Thread: SYSCONFIG

Tool/software:

Hi TI Experts,

Customer is working on SDK9.1. Customer is running Ethercat on ICSSG0 and their Sigmadelta on ICSSG1.

They have followed the below thread to configure the SYNC0.

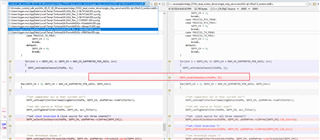

Their sysconfig configuration is shown below.

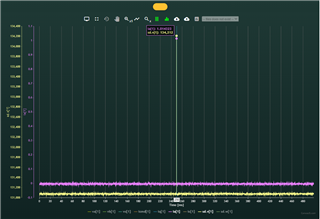

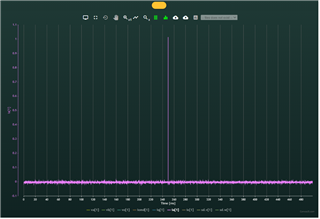

However, customer found that it will Failure to synchronize SYNC0 with PWM resulted in drift between SYNC0 and internal interrupts, along with sigma-delta current sampling noise and stalling.

Customer hopes to know if you could provide some guidance here.

Thanks,

Kevin