Part Number: LP-AM263P

Other Parts Discussed in Thread: SYSCONFIG

Tool/software:

Hi

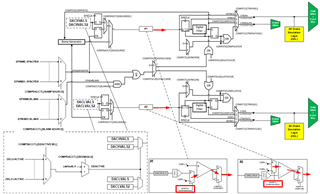

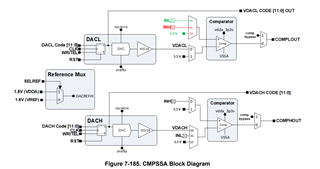

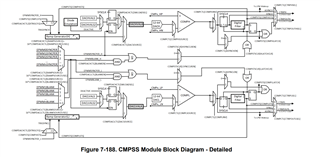

I'm reviewing AM263Px TI's technical reference manual for the CMPSS module, and I've come across two block diagrams. There are a few points I'm unsure about.

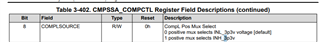

First, can the positive input of CompH and the negative input of CompL be configured? Or are they directly hardwired to the ADC input pins? Is it possible to configure either of them to use a fixed 3.3V reference? If so, how can that be done? Both COMPHSOURCE and COMPLSOURCE are only 1-bit wide, and I couldn't find any setting in SysConfig that allows selecting a 3.3V reference.

Second, in the block diagram, the COMPLSOURCE bit appears to control the negative input of COMPL. However, based on my review of the SysConfig options and the register documentation, it seems like it should be selecting the positive input instead. Has there possibly been a mistake in the diagram?

Regards,

Burak