Other Parts Discussed in Thread: SYSCONFIG, DP83869, CCSTUDIO

Tool/software:

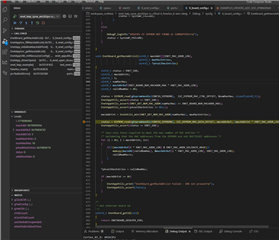

I have a TI sample project that mimics my company project scenario.

This may be an unlikely situation in the real world, but the fact that interrupts are not triggering may be indicating something is not properly set up with the interrupts that may cause errors down the road.

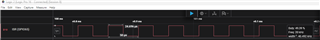

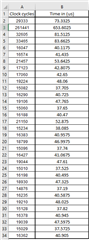

Basically I start of with TI's enet_lwip_cpsw project that sets up ethernet. I added PWM0 to run @ 40kHz and generate and interrupt every 2 cycles (@20kHz). The ISR executes for 50% of the CPU execution time. (This code will be moved to a nortos core that runs control code into an ISR. But for now it is running on core 0 for testing).

Inside PWMISR a pin is toggled and a long delay is done.

Also note, the PWM is configured up/down count mode during initialization, so PWM and ISR will execute very early.

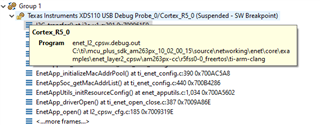

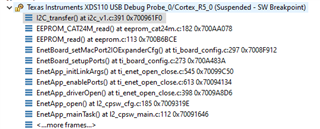

When I run this code, the enet initialization fails while trying to read the I2C EEPROM for MAC information.

EnetBoard_getMacAddrList calls EEPROM_read() 2 times. I2C_EEPROM_MAC_CTRL_OFFSET is successfull, but I2C_EEPROM_MAC_DATA_OFFSET fails during SemaphoreP_pend in I2C_transfer().

Here are some captures of registers from both calls to EEPROM_read():

- EEPROM_read(I2C_EEPROM_MAC_CTRL_OFFSET) before SemaphoreP_pend.

- EEPROM_read(I2C_EEPROM_MAC_CTRL_OFFSET) after SemaphoreP_pend.

- EEPROM_read(I2C_EEPROM_MAC_DATA_OFFSET) before SemaphoreP_pend. !!! never gets past SemaphoreP_pend

- Halted CPU to capture I2C registers.

I am surprised that I2C is not able to trigger the second time. Curious if it has something to do with I2C ISRs overflowing.

Any help would be appreciated to determine the exact cause and how to fix this situation. I am concerned it has to do with interrupt setup, that will become an intermittent issue later down the road.

Regards.

==================== How to reproduce the issue =======================

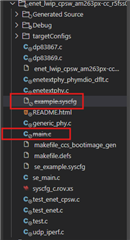

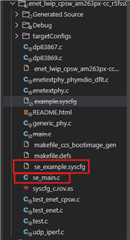

- Load project: mcu_plus_sdk_am263px_10_01_00_31\source\networking\enet\core\examples\lwip\enet_lwip_cpsw\am263px-cc\r5fss0-0_freertos

- overwrite the .sysconfig and main.c file.

- Run the project

- See non working output below

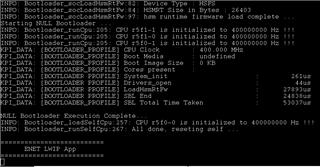

===================================LOGS=====================

### working output if PWM ISR is not using 50% CPU utilization when enet reads EEPROM

Starting NULL Bootloader ...

KPI_DATA: [BOOTLOADER_PROFILE] Boot Media : undefined

KPI_DATA: [BOOTLOADER_PROFILE] Boot Image Size : 0 KB

KPI_DATA: [BOOTLOADER_PROFILE] Cores present :

KPI_DATA: [BOOTLOADER PROFILE] System_init : 378us

KPI_DATA: [BOOTLOADER PROFILE] Drivers_open : 50us

KPI_DATA: [BOOTLOADER PROFILE] LoadHsmRtFw : 8584us

KPI_DATA: [BOOTLOADER PROFILE] SBL End : 3043us

KPI_DATA: [BOOTLOADER_PROFILE] SBL Total Time Taken : 12057us

NULL Bootloader Execution Complete...

==========================

ENET LWIP App

==========================

EnetAppUtils_reduceCoreMacAllocation: Reduced Mac Address Allocation for CoreId:0 From 4 To 2

Link Status Changed. PHY: 0x0, state: up

Open MAC port 2

EnetPhy_bindDriver: PHY 0: OUI:080028 Model:0f Ver:03 <-> 'DP83869' : OK

PHY 0 is alive

Starting lwIP, local interface IP is dhcp-enabled

[LWIPIF_LWIP] NETIF INIT SUCCESS

Host MAC address-0 : 70:ff:76:1f:61:88

[LWIPIF_LWIP] Enet has been started successfully

[0]status_callback==UP, local interface IP is 0.0.0.0

UDP server listening on port 5001

Cpsw_handleLinkUp: Port 2: Link up: 1-Gbps Full-Duplex

MAC Port 2: link up

[0] link_callback==UP

5. 69s : CPU load = 3.63 %

### NON WORKING output if PWM ISR IS using 50% CPU utilization when enet reads EEPROM

### LWIP init halted trying to read I2C EEPROM

Starting NULL Bootloader ...

KPI_DATA: [BOOTLOADER_PROFILE] Boot Media : undefined

KPI_DATA: [BOOTLOADER_PROFILE] Boot Image Size : 0 KB

KPI_DATA: [BOOTLOADER_PROFILE] Cores present :

KPI_DATA: [BOOTLOADER PROFILE] System_init : 378us

KPI_DATA: [BOOTLOADER PROFILE] Drivers_open : 50us

KPI_DATA: [BOOTLOADER PROFILE] LoadHsmRtFw : 8584us

KPI_DATA: [BOOTLOADER PROFILE] SBL End : 3042us

KPI_DATA: [BOOTLOADER_PROFILE] SBL Total Time Taken : 12054us

NULL Bootloader Execution Complete...

==========================

ENET LWIP App

==========================