Part Number: AM2634

Does AM2634 support self interrupt nesting?

example:

_interrupt EpwmIsr()

{

//do some task

(breakpoints)

while(1)

{

;

}

//clear relative flags

}

if I add a break point before while(1), the program can always stop at that break points instead of just once because interrupt will nest itself

-----------------------------------------------------------------------------------------------------------------------------------------------

why I choose this way(self interrupt nesting)?

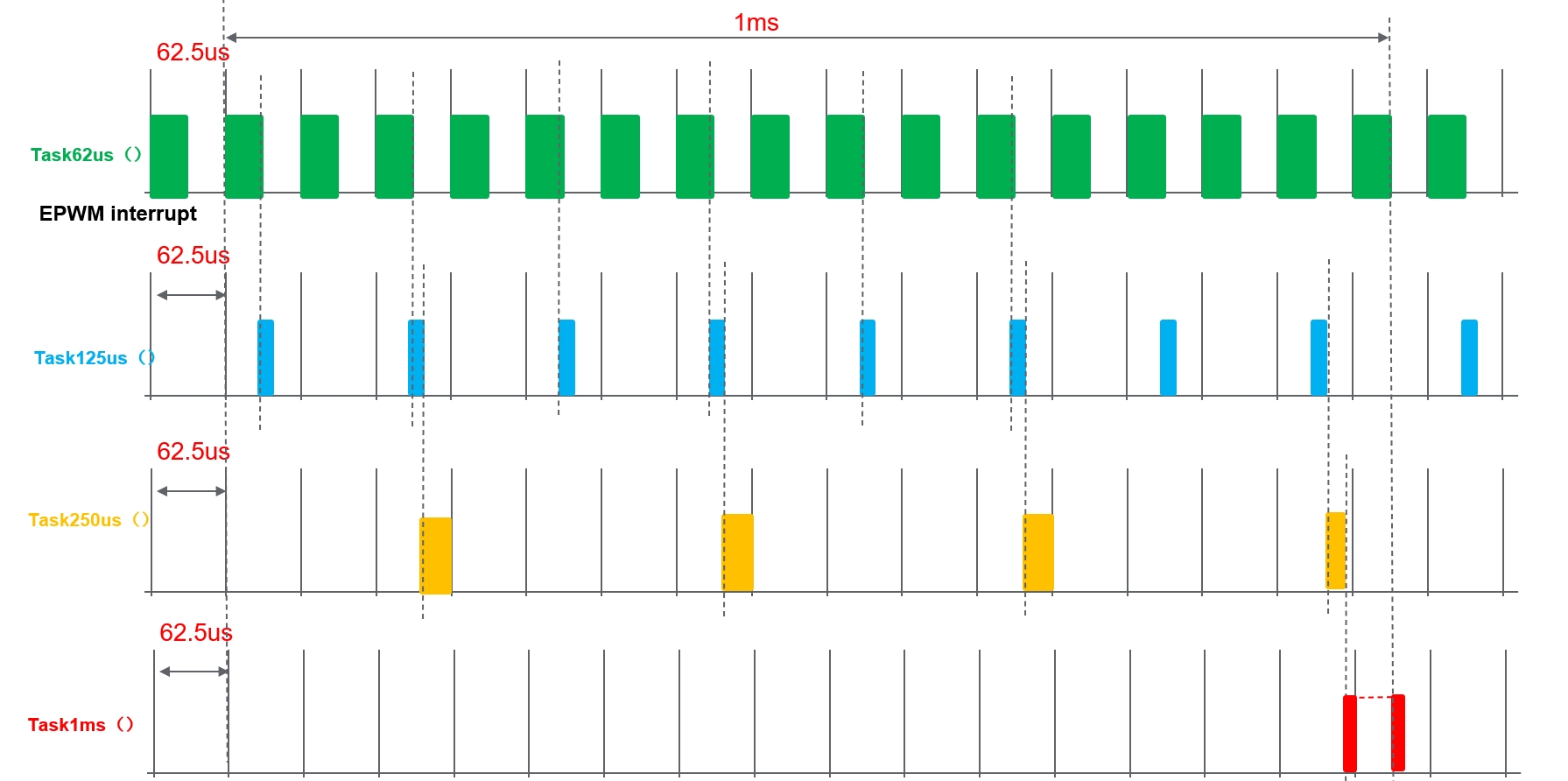

assume my work now have 4 types of tasks: 62.5us/125us/250us/1ms task.

run my 62.5us task need 30us, but 125us 250us 1ms need time more than 32.5us, so i cant finish all my function within 62.5us, but 125us /250us /1ms don't need to execute every 62.5us

my solution

_interrupt 62.5us service()

{

62.5cnt = (62.5cnt++ &0x0f) //make sure 62.5cnt range in 0~15

//always do 62.5us task

//if (62.5cnt & 0x01) do 125us task

//if (62.5cnt & 0x03) do 250us task

//if (62.5cnt & 0x0f) do 1ms task

}

so in this way I can only use 1 interrupt ISR rather than 4 different priority ISRs can finish my work.

-----------------------------------------------------------------------------------------------------------------------------------------

Above all, is 2634 support self interrupt nesting? how do I configure it?